工具与软件:

您好!

我在轻负载条件下遇到 UCC28950PWR 问题。

- 开关频率显著提高(例如、1.5A 负载下为~298kHz)、从而导致出现大浪涌。 这种行为的根本原因可能是什么?

- 是否有推荐的方法可用于减轻轻负载下的这些浪涌?

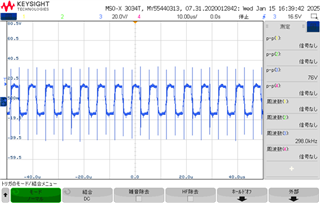

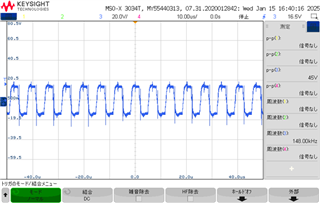

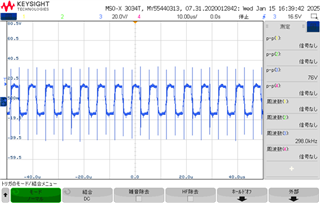

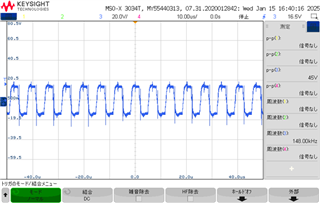

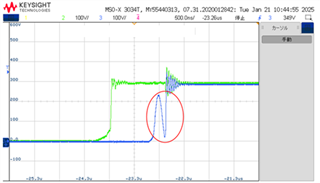

随附了供参考的 FET 栅极波形:

- 附件1:1.5A 负载(频率~298kHz)

- 附件2:3A 负载(频率~148kHz)

非常感谢您提供有关理解和解决此问题的指导。

谢谢!

Conor

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我在轻负载条件下遇到 UCC28950PWR 问题。

随附了供参考的 FET 栅极波形:

非常感谢您提供有关理解和解决此问题的指导。

谢谢!

Conor

尊敬的 Mike:

感谢您的回答。 我还有一个问题。

我可以看到一个波形、其中 VDS 在负载较轻时下降一次。 您知道为什么会发生这种情况吗? 我将向您发送 VDS 波形信息、因此请您检查一下。

e2e.ti.com/.../VDS-waveform-information.xlsx

谢谢!

Conor

尊敬的 Mike:

感谢您的检查。 我期待您的意见。

我还有一个关于 RAB 和 RCD 值的额外问题。

为了简化设计、数据表指出 RAB 和 RCD 通常设置为相同的值。 但是、我想知道是否有建议为这些电阻设置不同值或为这些电阻设置不同值的具体情况或设计场景。

具体而言:

在特定条件(例如负载变化、MOSFET 特性或拓扑)下、不同的值是否会提高系统效率或 ZVS 性能?

将 RAB 和 RCD 设置为建议范围(13kΩ–90kΩ)内的不同值时、是否存在任何限制或注意事项?

谢谢!

Conor

您好!

就 VDS 波形而言、它看起来没有 正确设置 RDELAB 和 RDELCD。 导通延迟应是谐振回路频率的1/4。 以下链接将为您提供一份应用手册、其中展示了如何使用固定延迟方法设置这些延迟时序。

https://www.ti.com/lit/an/slua560d/slua560d.pdf

感谢您关注德州仪器(TI)产品。 如果您有相关问题、请点击右上角的"提出相关问题"按钮。 新创建的问题将自动链接到此问题。

此致、