工具与软件:

尊敬的论坛:

我想问 PC2比较器 HF CD74HC4046A 是否无死区?

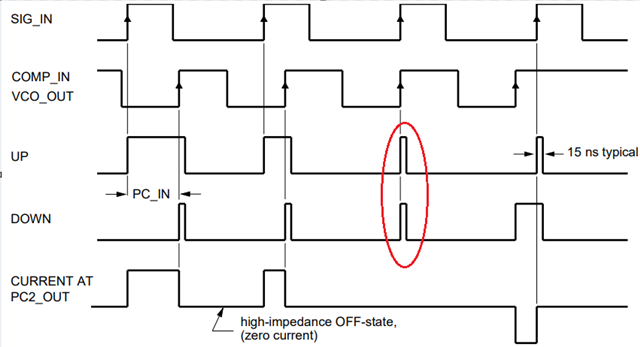

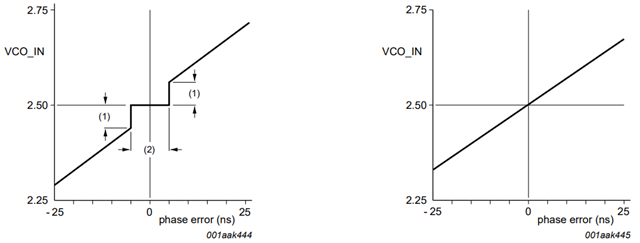

PC2具有树态电压输出、并在 PLL 达到锁定状态时(相位差为0度)进入 Hi-Z 状态、生成小芯脉冲后、最好是校正脉冲

也非常小(比逻辑门的 tpd 小~)、确保在整个调谐范围内具有恒定的灵敏度、而不会出现突变)。

74HCT9046A (不再生产) 展现了通过电流输出和 内部"向上"和"向下"拉电流/灌电流在短时间内同时导通的技术所实现的"无死区"功能。

尽管 CD74HC4046是一个电压输出器件(然而、FET 电流限制~电流发生器)、但它是否有可能具有类似的功能(抗反冲时间->内部 D 触发器异步复位延迟~ 10..15ns)? 因为 TI 文档 SCAA088使用4046A 的 PC2来满足低相位噪声要求。

此致、

Joseph