工具与软件:

尊敬的专家:

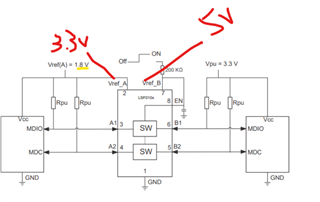

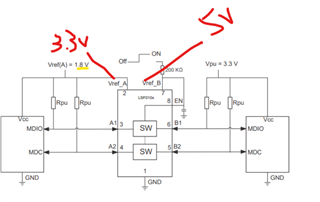

针对该有关 在 FPGA (3.3VDC)和外部器件(5VDC)之间充当电压转换器的 LSF0108PWR 的疑问提供帮助:

问题是、如果在转换器引脚 A (侧)和 B (侧)上分别使用1k 上拉电阻作为数据线。 影响将是什么?

a)如果是下行转换?

b)如果是向上转换?

谢谢你。

73,

阿奇·A·.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的专家:

针对该有关 在 FPGA (3.3VDC)和外部器件(5VDC)之间充当电压转换器的 LSF0108PWR 的疑问提供帮助:

问题是、如果在转换器引脚 A (侧)和 B (侧)上分别使用1k 上拉电阻作为数据线。 影响将是什么?

a)如果是下行转换?

b)如果是向上转换?

谢谢你。

73,

阿奇·A·.

您好、Archie:

LSF 外部上拉电阻的大小基于根据您的系统要求进行的速度/功率权衡。 由于 RC 时间短、更强的上拉电阻支持更高的 DR、尽管这也意味着额外的电流会灌入驱动器侧。

这组 Logic Minute 视频可进一步对此进行说明:https://www.ti.com/video/series/understanding-the-lsf-family-of-bidirectional--multi-voltage-lev.html

a)下行转换将是5V 至3.3V、输出端的上升时间将是使用电容器的1k Ω 上拉电阻。 负载的负载。 如果推挽驱动器/接收器、也可以移除该输出侧的上拉电阻器。

b.)上行转换为3.3V 至5V。 此处需要上拉、强上拉导致的估计 VOL 等于 VOL = VIL + IOL x RON、其中 IOL 是通过 B 侧和 A 侧外部上拉电阻灌入的电流。

此致、

插孔