工具与软件:

大家好、团队成员:

该 E2E 主题

客户执行更多测试来重现 GLA 对地短路故障。

它们使用3倍控制模式、并使用4.7nF 至10nF 的外部 Cgs 进行测试、Cgs 更高、触发短路的概率更高。

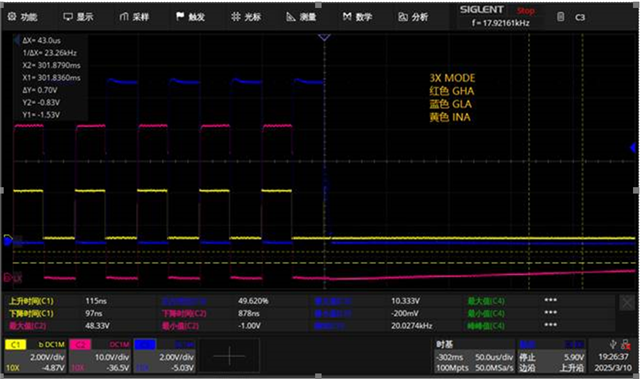

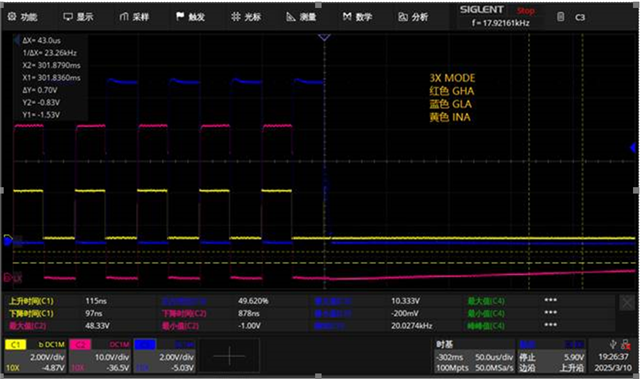

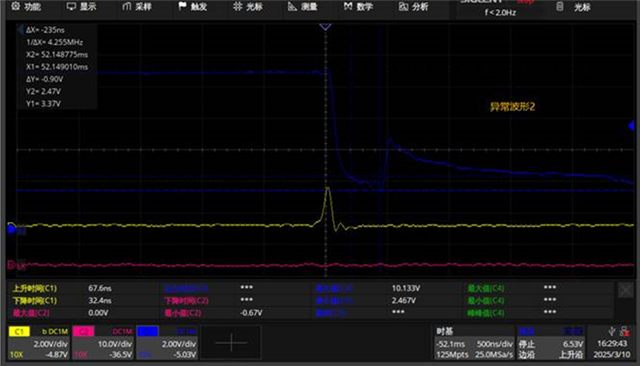

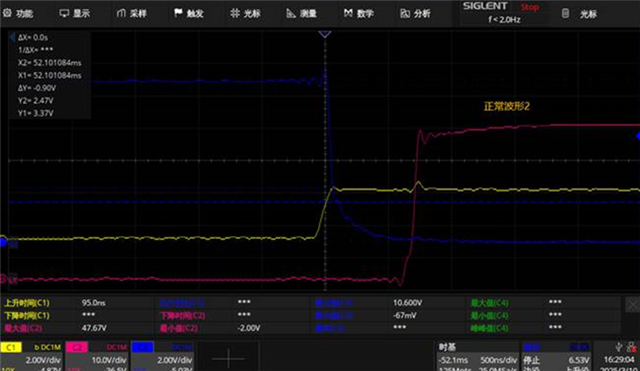

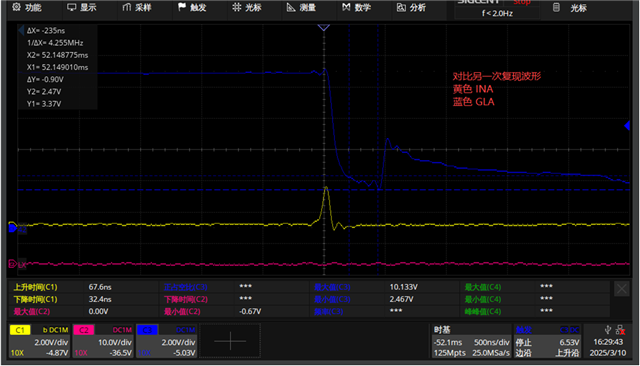

黄色:INA、蓝色:GLA、红色:GHA

故障图1:

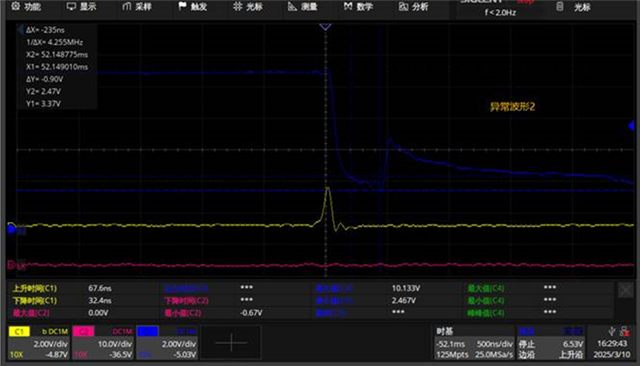

故障图2:

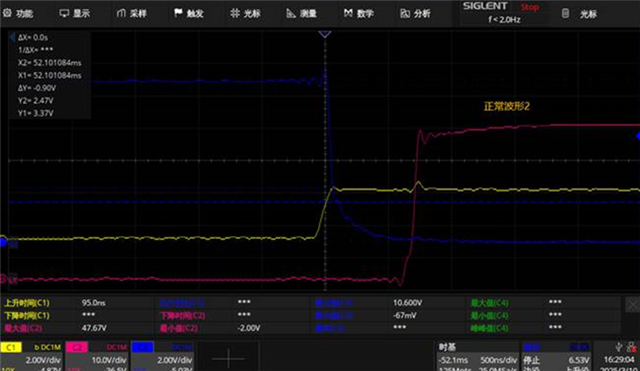

正常图1:

从故障图中可以看出、在非常窄的 INA 脉冲中、GLA 将在下降沿对地短路、客户不认为是负电压问题。

请帮助找到根本原因。

谢谢!

Yishan Chen

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

大家好、团队成员:

该 E2E 主题

客户执行更多测试来重现 GLA 对地短路故障。

它们使用3倍控制模式、并使用4.7nF 至10nF 的外部 Cgs 进行测试、Cgs 更高、触发短路的概率更高。

黄色:INA、蓝色:GLA、红色:GHA

故障图1:

故障图2:

正常图1:

从故障图中可以看出、在非常窄的 INA 脉冲中、GLA 将在下降沿对地短路、客户不认为是负电压问题。

请帮助找到根本原因。

谢谢!

Yishan Chen

大家好、团队成员:

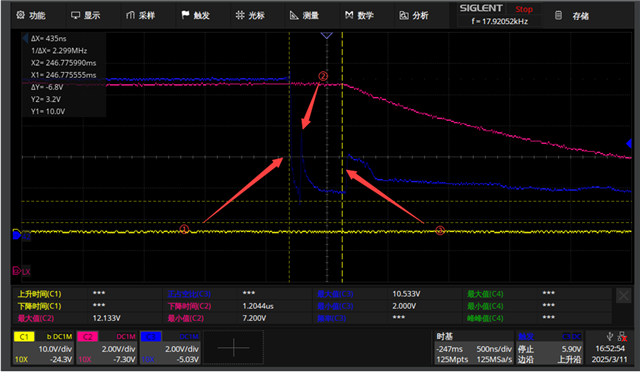

添加故障流程

1. INA 产生极高/极低占空比、极短的下降沿

2.一旦栅极下拉时间达到100ns、INA 会从高电平信号转为下降沿、此时会出现上升电压尖峰。

3、约300nS、栅极具有另一个上拉电压尖峰、VGLS 下拉至2.5V、驱动器报告故障

4.他们测试驱动器引脚、发现低电平 FET 对地短路

他们认为是因为上 FET 和下 FET 在输出驱动器级同时开路、从而导致该故障。

黄色:相电压、蓝色:GLA、红色:VGLS

黄色:INA、蓝色:GLA

您能否查看此紧急问题并向客户提供一些反馈?

谢谢!

Yishan Chen

尊敬的 Yishan:

我们认为发生的情况是、 由于在对低侧栅极发出另一条"导通"命令之前未提供足够的时间使低侧栅极完全关断、因此 GLx 上可能出现绝对最大/最小值违例。

由于占空比非常低、在 发出另一条开启 GLx 的命令之前、从 GLx 至 SLx 的电压无法完全达到0V。 我们认为这是导致损坏的原因、因为在发出新命令再次开启 GLx 时、由于布线的电感、仍然存在灌电流。 Cgs 电容值会增加 GLx 电压达到0V 所需的时间、从而增加实现有效高侧导通所需的最小占空比%。

所以对于客户:请让他们在器件的 GLA 引脚处探测并重复测量。 我们需要 在器件引脚不靠近 MOSFET 的位置测量 GLA 的电压。 另请将探头的接地端置于器件接地端。 我们认为、如果在靠近器件引脚的位置进行测量、我们可能会看到更高的电压尖峰、这可能会损坏器件。

高侧实际上能够导通的最低占空比%输入是多少? 高侧输入命令必须足够长、以便为低侧完全关断和高侧导通提供足够的时间。 因此、控制软件不应允许向高侧发送低于最小占空比百分比(高侧实际开启的情况)的高侧发送占空比输入。

低侧也是如此。 客户应确保在高占空比%时、确保低侧有足够的时间实际开启。

谢谢!

Joseph

尊敬的 Yishan:

我理解。

以下是一些硬件修改可尝试解决该问题:

1.增加布线宽度。 我不知道客户的电流布线宽度是多少、但采用更宽的布线可能会对问题有所帮助。

2.我知道您提到客户测试的 Cgs 4.7nF 到10nF。 并且在10nF 时更有可能发生问题。 他们是否尝试使用低于4.7nF 的 Cgs? 或许较小的 Cgs 值可以解决该问题。 客户可以测试低于4.7nF 的不同值、看看其结果是否更好。

如果硬件修改无法解决问题、那么我建议对最小占空比施加软件限制、以确保正确运行。

谢谢!

Joseph