工具/软件:

您好!

我目前正在对基于 DRV2700EVM-HV500的 DRV2700定制实现方案进行故障排除。 除了一些关键差异外、我的设计几乎可以根据参考设计完全实现:

- 我使用一个基于 ETD29磁芯且间隙为0.9mm 的定制绕组反激式变压器。 初级绕组为15匝、次级绕组由4 x 93匝串联形成、总输入输出匝数比为1:25。

- 每个次级绕组都有一个 S8CMHQ 反激式二极管和10nF 3kV 陶瓷电容器。

- 我测量了19.5uH 处的初级电感

- 我使用的 MOSFET 额定电压高于 EVM - IXTA02N250HV。

- 我的反馈电阻器是:20兆欧、1千欧和10千欧。

- 我的下部反馈电阻器由介于0V 和1.3V 之间的运算放大器驱动、以在0kV 至~2kV 之间调节 HV 输出。

当我尝试将输出电压驱动至超过1kV 时、我会发现 FB 引脚上的电压会下降、输出电压不再升高。 我注意到、在探测 SWITCH 引脚时、PWM 占空比设置超过~ 55 (超过导致 V_FB 下降的占空比)、DRV2700似乎以大约90%的占空比驱动控制器。 我是否已经达到了 IC 在这里可以执行的操作的限制?

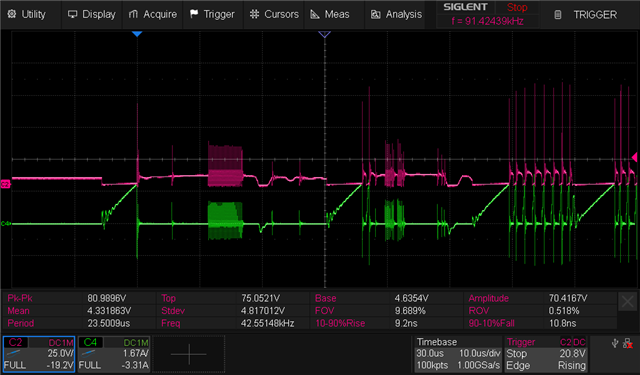

前两个屏幕截图是我配置了 PWM 占空比、使得输出电压为650V。 转换器在以下模式下运行:在 SW 节点(通道3)上出现脉冲突发。 通道1上显示输出电压。 第二个屏幕截图是开关事件的特写。占空比约为90%。

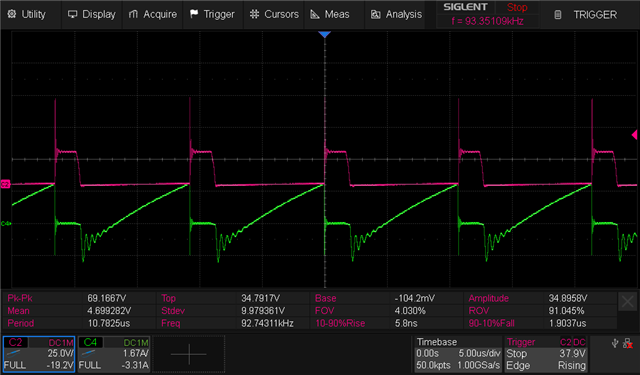

接下来的两个屏幕截图是当 I 将 PWM 占空比增加到55 (本例中为50)以上时、此时输出电压不再增加、FB 引脚电压会下降。 输出电压要更加稳定、大约1kV、SW 节点看起来非常相似。 此模式的不同之处在于没有脉冲跳跃、SW 节点持续以大约90%的占空比开关:

目前、输出负载为大约13M Ω 的电阻、外加一个 MISIG 隔离式差分示波器探头 DP3002 (额定电压为3kV)。 输出端还有10nF 的旁路电容。 REXT 值设置为6k Ω(最小建议值)。

提前感谢您的帮助。