主题: DRV8353中讨论的其他器件

工具/软件:

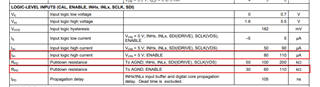

在 DRV8340-Q1数据表中、对于使能引脚、输入逻辑高电平电流(I_LH)被称为80uA (在5V 输入时)和60k Ω 的下拉电阻(内部下拉)。

如果我计算下拉电流、则该值为83.33uA。 为什么不匹配? 内部运算放大器的剩余偏置电流是否为-3.33uA?

如果在 VM > UVLO 的情况下使能引脚悬空、会导致使能引脚上出现0.2V (3.33u*60k)吗?

否则、为什么输入逻辑高电流和下拉电阻不匹配。 (它与 INHx、INLx 引脚输入逻辑高电平电流和下拉电阻匹配)。

以上查询与典型值相关。

对于最大输入逻辑高电平电流值、所有引脚逻辑高电平电流与下拉电阻不匹配。 (I_IH_max = 90uA 且 R_PD_min = 50k Ω、即 I_pin = 5/50k = 100uA)

对于 TI 的其他栅极驱动器、像 DRV8353这样的数据表中不会观察到这种不匹配情况。

请解释数据表中提到的引脚输入逻辑高电平电流值以及计算出的下拉电阻电流的原因。

典型值和最大值的计算温度。

谢谢你。