工具/软件:

您好专家、

客户遇到 DRV3946 的两个问题:

1. INIT2 阶段后是否会进行 NAD 检测?

2.当 NAD_OVERRIDE = 1 时、为具有 NAD 错误的器件分配了 NAD。 但分配的 NAD 和 NAD_OVERRIDE 位于同一寄存器中。 客户应该单独编写还是写入一次?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好专家、

客户遇到 DRV3946 的两个问题:

1. INIT2 阶段后是否会进行 NAD 检测?

2.当 NAD_OVERRIDE = 1 时、为具有 NAD 错误的器件分配了 NAD。 但分配的 NAD 和 NAD_OVERRIDE 位于同一寄存器中。 客户应该单独编写还是写入一次?

您好、北大、

感谢您的提问

以下是我的评论

[quote userid=“572795" url="“ url="~“~/support/motor-drivers-group/motor-drivers/f/motor-drivers-forum/1522419/drv3946-q1-nad_error-detection INIT2 阶段后是否会进行 NAD 检测? [/报价]在 NORMAL 模式下、NAD 检测不会在 INIT2 之后完成。 如果器件 REINIT_NAD 中存在 NAD_ERR、则可以执行 NAD-INIT。

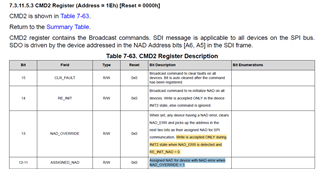

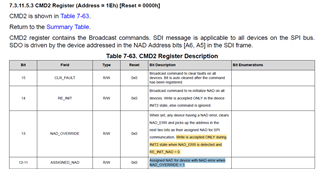

[quote userid=“572795" url="“ url="~“~/support/motor-drivers-group/motor-drivers/f/motor-drivers-forum/1522419/drv3946-q1-nad_error-detection 当 NAD_OVERRIDE = 1 时、为具有 NAD 错误的器件分配了 NAD。 但分配的 NAD 和 NAD_OVERRIDE 位于同一寄存器中。 客户应该单独编写还是编写一次?两个寄存器字段应一起写入一次。

谢谢、

Ibinu

Ibinu,

新问题:DRV3946-Q1 进入运行状态后、它们尝试关断 PVDD 并保留 VDD。 在这种情况下、它们需要关闭继电器。 因此、它们的运行方式如下:

1、客户发送 CMD1 (CLR_FAULT=1 且 CH1_CTRL = 0) 且读取 CH1_STAT 仍为 0x5。

2.等待几秒钟、它们会重试发送 CMD1 (CLR_FAULT=1 且 CH1_CTRL = 0)、并且读取 CH1_STAT 为 0x0。

对于两种操作、PVDD 始终为 UV。 客户想知道 PVDD_UV 之后是否有内部延迟、以便 CH1_STAT 无法更改? 或者、它们是否需要发送 CLR_FAULT=1、然后发送 CH1_CTRL=0 以更改 CH1_STAT、而不是一起发送两条命令?