工具/软件:

尊敬的专家:

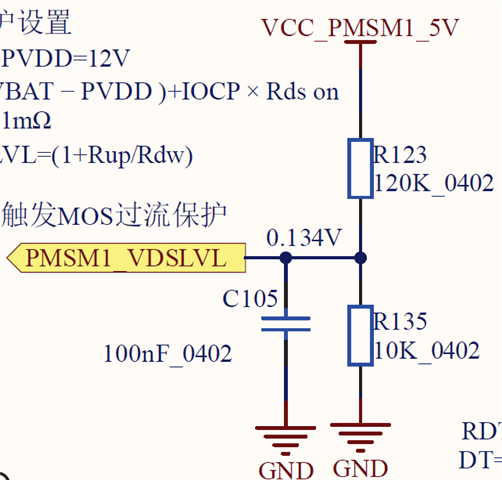

我的客户端目前使用 DRV8329、当电路在没有负载的情况下上电时、MCU 提供驱动信号、但器件无法运行、nFAULT 引脚保持被拉至低电平。 经过调查后、禁用 VDS 过流保护功能(通过使用 100kΩ 电阻器将 VDSLVL 连接至 GVDD。) 允许器件恢复正常运行。

测试后、MOSFET 开通时间约为 500ns、负载电流为 0。 我想知道

1.导致 nFAULT 引脚持续被拉低的原因。

2.目前、禁用 VDS 过流保护可以让电路恢复运行、但会失去过流保护功能。 如何改进这一点?

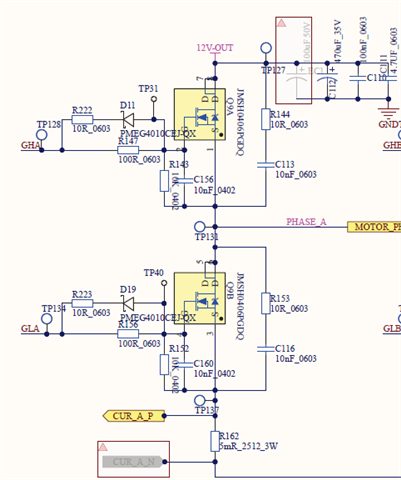

下面是一些原理图:

VDSLVL

驱动电路