“Thread:Test, DRV8312”中讨论的其它部件

你好,支持团队。

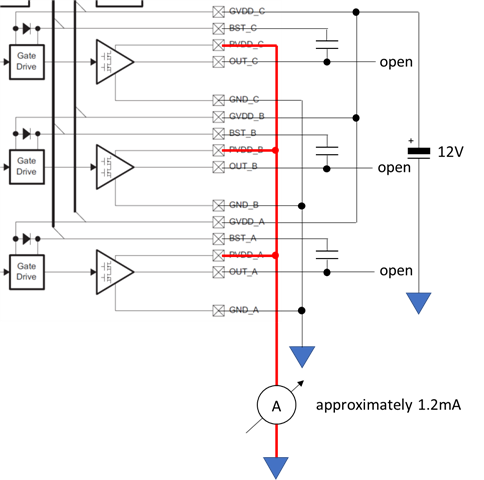

我的客户正在尝试查看 PVDD_x 的泄漏电流

(有关电路图,请参阅下图。)

他们报告 PVDD_x 的总泄漏电流约为1.2mA。

此当前值是否为预期值?

它们还确保1.2mA 始终流动。

此致,

希加

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好,支持团队。

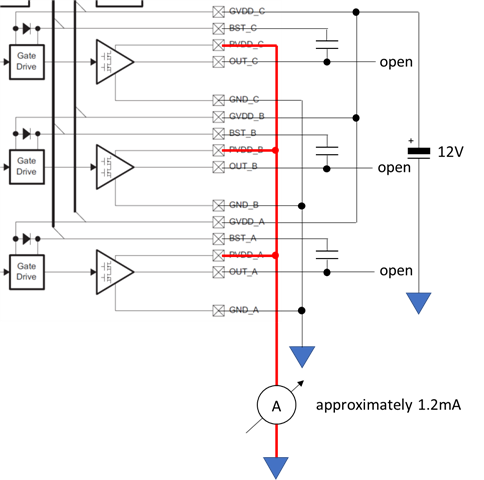

我的客户正在尝试查看 PVDD_x 的泄漏电流

(有关电路图,请参阅下图。)

他们报告 PVDD_x 的总泄漏电流约为1.2mA。

此当前值是否为预期值?

它们还确保1.2mA 始终流动。

此致,

希加

Daisuke 您好,

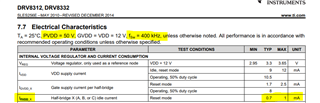

这似乎与数据表中的规格一致。 您正在测量的是 SPEC IPVDD_X (PVDD 闲置电流),在数据表中,400kHz PWM 频率和 PVDD = 50V 时,每半桥的电流通常为0.7mA。 由于这是一个非常低的 PVDD 值,泄漏电流应小于每半桥0.7mA。

不幸的是,我们没有 IPVDD 与 PVDD 的特征曲线,所以当 PVDD 为12伏时,我无法确认 IPVDD_X 的正确值,但较低的值与我的预期一致。

谢谢,

亚伦

是否要将 PVDD 连接到 GND? 发生这种情况的唯一方法是,如果集成 FET 中有内部直通电流,如果 PCB 设计良好,且在输出_x 路径中没有增加电感,则应降低该电流。 由于当前路径不适用于 out x,因此不应有电流流动的当前路径,因此这不会影响驱动器中的门开关。 HS 和 LS FET 之间也插入了很小的死时间,因此不应存在通过电流射向的风险。

如果有任何问题,过电流保护应保护设备在直射条件下的安全,并保护内部 FET 的 Hi-Z -这意味着唯一的漏电流路径是已经测量的 PVDD 路径。

谢谢,

亚伦

Daisuke-San,您好!

客户是否在测试泄漏电流时确保半桥关闭?

https://e2e.ti.com/support/motor-drivers-group/motor-drivers/f/motor-drivers-forum/1008722/drv8312-current-leakage-to-pvdd

我需要看看我们是否有执行此测试的工作台能力。

谢谢,

亚伦

Daisuke-San,您好!

我只能使用 EVM 上 PVDD 引脚中的 DMM 测量电流。 它可能来自 PVDD_x (每个相的 PVDD 引脚0.4 mA),但我无法具体测量 EVM 上的每个电流。 我没有测试特定引脚的工作台能力。

我发现了一条与客户所要求的内容完全相同的旧线程: https://e2e.ti.com/support/motor-drivers-group/motor-drivers/f/motor-drivers-forum/307780/drv8332---leak-current-from-vdd-gvdd-pin-to-pvdd-pin

由于数据表中没有电源关闭序列,因此可以通过以下方法消除漏电流:

-在 PVDD 之前卸下 GVDD

-设置 reset_x =1和 PWM_x =0以屏蔽泄漏电流

谢谢,

亚伦