你好

我目前正在使用DRV 8412,我的应用程序仅用于双向电流控制。 首先,我想问一下,我们是否可以单独使用所有的半桥?

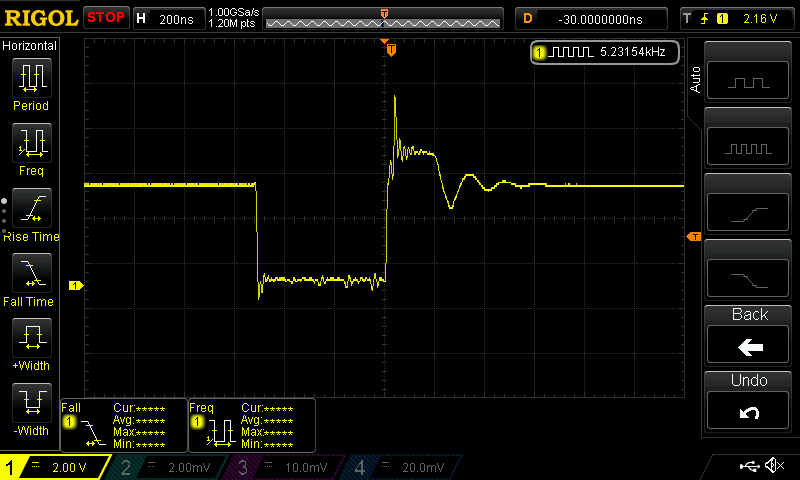

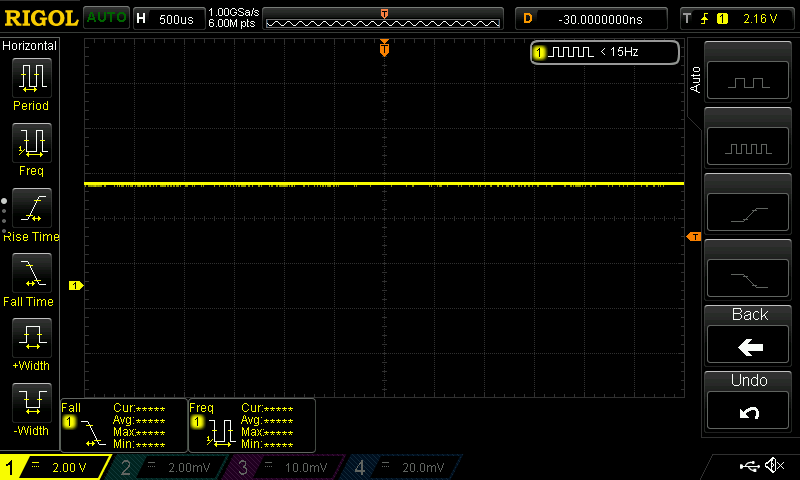

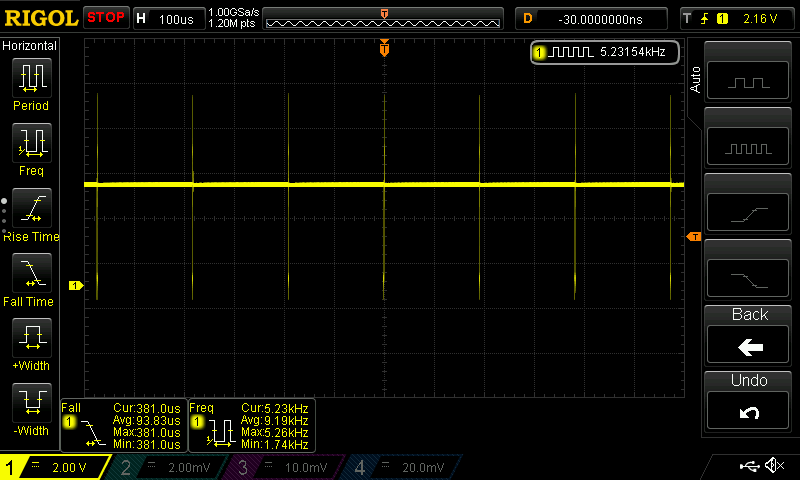

其次,当我在A的高侧MOSFET和B的低侧MOSFET上保持一个H桥接时(在不切换的情况下永久打开),然后在将负载增加到0.85 A或以上之后,OUT_A输出不是恒定的。 波形显示它正在尝试关闭A的高侧MOSFET。我正在附加波形。 第一个波形是放大版本的第三个波形。 第二个波形是高侧MOSFET的正常操作(发生在0.85 A负载电流以下)。

第三,当PVDD_X引脚处提供恒定电压且PWM_X设置为逻辑1时,OUT_X引脚处的输出电压会增加。 0.5 V的OUT_X引脚处的电压升高。例如,如果PVDD_A被提供6 V,则我在6.5 V的OUT_A处接收输出