您好!

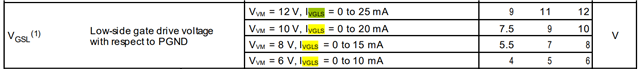

我们只是想知道 Vgls 稳压器是如何工作的、因为它可能会损坏我们的 FET。 数据表中确实给出了 VM > 12V 时的规格 Vgl... 我们的 VM 最高可达35V、我们希望确保 Vgls 不超过20V ...

我看到另一个话题、5年前有人提出类似的问题、但没有人回答。

此致、

Jerome

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好 Jerome、

VGLS 是由 VM 供电的内部稳压器。 对于低侧栅极驱动器电源、VGLS 通常为10-12V 输出。 您可以使用更高的 VM 电源电压、而 VGLS 稳压器上的压降将会更大、从而导致更多的功率耗散。

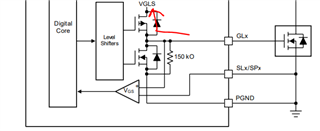

目标是确保 VGLS 不会反向供电到 VM。 VGLS 输出不应超过20V、因此应实施适当的 VGLS 注意事项、例如将 VGLS 旁路电容器靠近器件放置、使用适合的 IDRIVE 设置为 VGLS 旁路电容器使用额定电压为25V 的电容器、 并确保 GLX 上不会出现电压尖峰、从而使其不会穿过下面的体二极管路径。

希望这对您有所帮助、

Aaron

您好!

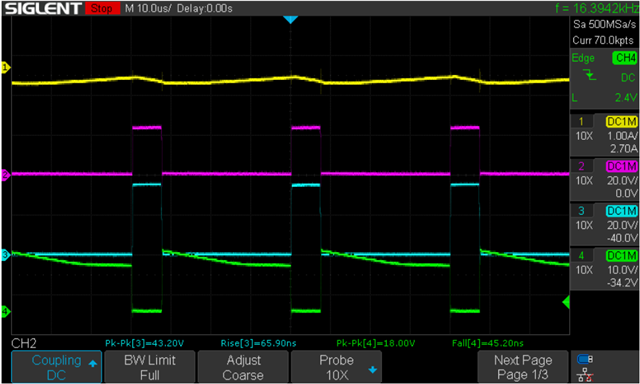

我在 DRV8323的评估过程中进行了相当多的测试、使用24V 的 VM 时、我看到 GLx 范围介于12V 到18V 之间、具体取决于我所做的测试。 但它看起来是 IDRIVE 电流选择量的函数。 这让我相信、18V 的跳变可能是栅极驱动器和 FET 之间的迹线电感造成的。

这是采用最高栅极 IDRIVE 设置时的情况

CH1:IOUTA、CH2:VOUTA、CH3:GHA、CH4:GLA

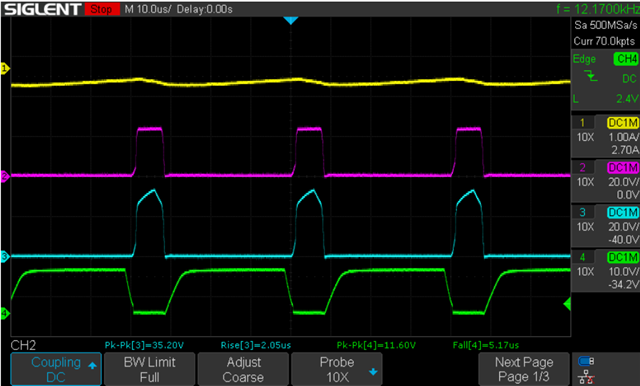

这是采用最低栅极 IDRIVE 设置时的情况

CH1:IOUTA、 CH2:VOUTA、 CH3:GHA、 CH4:GLA

但是、如果 Vgls 的 LDO 真正设置为不超过12V、那么这就是我需要知道的。 从数据表中可以看出、Vgls 是通过 VM 进行缩放的...

此致、

Jerome

您好 Jerome、

如果您的 IDRIVE 设置过高 、并且栅极驱动输出中存在高迹线电感、 然后、由于公式 V = L * di/dt、高 IDRIVE 设置可能会导致栅极驱动电流(di/dt)的变化过高、因此如果栅极驱动输出(L)中的电感过大、这可能会导致电压(V)增加。

从下面的 IDRIVE 设置中、您可能需要根据 MOSFET 的 Qgd 值和根据栅极驱动器布局可支持的栅极驱动电流大小、选择合适的 IDRIVE 设置值。

如需更多信息、请参阅此 E2E 常见问题解答: e2e.ti.com/.../faq-selecting-the-best-idrive-setting-and-why-this-is-essential

谢谢、

Aaron