主题中讨论的其他器件: CSD19536KTT、 CSD18531Q5A

我有 DRV8353的 SPI 版本。

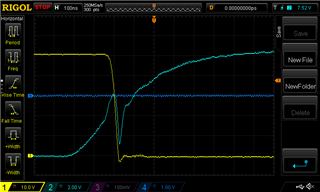

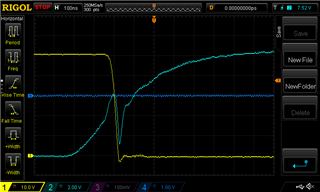

在3x 模式下驱动单个 H 桥时、当高侧栅极最终降至0V 时、我会看到低侧栅极上的电压下降。 在下图中、黄色是高侧栅极、青色是低侧栅极。

这在过去的1x 模式中明显没有发生过。 H 桥的电源电压相同(48V)。 我根本没有更改我的板。 3倍模式与1倍模式是否有什么不同的情况会导致这种情况发生? 无论如何、我如何缓解这种情况?

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我有 DRV8353的 SPI 版本。

在3x 模式下驱动单个 H 桥时、当高侧栅极最终降至0V 时、我会看到低侧栅极上的电压下降。 在下图中、黄色是高侧栅极、青色是低侧栅极。

这在过去的1x 模式中明显没有发生过。 H 桥的电源电压相同(48V)。 我根本没有更改我的板。 3倍模式与1倍模式是否有什么不同的情况会导致这种情况发生? 无论如何、我如何缓解这种情况?

谢谢!

您好、Alcor、

我猜此时电流将流入 SHX、因此低侧栅极的导通会导致 SHX 从 VM+0.7V 降至接地。 高侧 MOSFET 完全关闭、但 MOSFET 的源极为 VM+0.7V、因此栅极也为 VM+0.7V。

1xPWM 可实现梯形控制、通常由流出 SHX 的电流控制。 如果您刚刚切换到正弦或 FOC 控制、则将有一半的时间电流从 SHX 流出、另一半的时间电流流入 SHX。 现在、您似乎 需要担心电流会流出并流入 SHX。

当电流仅从 SHX 流出(如在1x PWM 中)时、SHx 的下降时间由高侧 MOSFET (IDRIVEN_HS)的关断控制。 正如我在上面注释的那样、当电流流入 SHx 时、这意味着低侧 MOSFET 的导通控制 SHx 的下降时间(IDRIVEP_LS)。

它看起来非常快的下降时间让 IDRIVE 不知所措。 SHx 上的负边沿通过 MOSFET 的 CGD (寄生电容器)从 MOSFET 栅极吸出电荷的速度快于 IDRIVE 对其进行补充的速度、至少需要一小段时间。 如果可能、请尝试减小 IDRIVEP_LS 以查看它是否会减少振铃。

谢谢、

Matt

我们遇到的一个问题是使 FET 运行得足够快。 如果可能、我们不希望减少 IDRIVEP、因为这将使 FET 导通时间更长。 我们还可以采取其他措施吗?

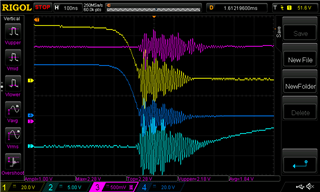

此外,我在1x 模式下看到了高电流振铃--这是否出于同样的原因?

黄色=高侧、青色=低侧、粉红色=电流放大器输出(SOB)、蓝色=开关节点/相位。 这对我来说有点像示波器拾取、因为所有波形都有、而且我们在 SOB 上有一个输出滤波器、该滤波器不应允许这种频率。 我们以前看到过它会杀死噪声。 你怎么看?

嘿、Alcor、

当您说在使 FET 足够快时遇到问题时、您的目标上升/下降时间是多少? 您要切换多少电流?

我们有一个有关 大功率电机驱动器应用系统设计注意事项的常见问题解答。

我们还提供 了一个了解智能栅极驱动的页面。

这些资源可能会对您有所帮助、便于您查看。

至于噪声、示波器噪声通常在10Mhz 范围内、而 EMI 噪声通常在1MHz 范围内。

如果您认为您的原理图会有所帮助、我可以帮您进行审阅。

谢谢、

Michael

我们需要在栅极上放置30nF 的电容来阻止低侧 FET 的 dv/dt 导通--如果没有它,在高侧导通期间,低侧栅极上会出现大电压跳转,这会导致击穿。 这是一个问题、它在增加额外的电容后消失了。 现在我们有47nF、这有点高、但20:1经验法则告诉我们、对于我们使用的 FET、我们将需要30nF。 因此、由于我们需要的电容数量、现在很难使信号的上升和下降时间超过1us。 因此、我们无法真正降低驱动电流。

该噪声大约为100MHz。 这非常快、我无法想象它可以打开 FET。 当然、您可以查看原理图、但我们可以在 PMS 中执行它吗?

您好、Alcor、

它是否与4个月前讨论的设计相同?

您能告诉我们您使用的是什么晶体管吗? 其中一些不适用于高速开关、而是用于电子保险丝应用等 我会尝试2或3种其他类型、并检查它是否有助于防止 dv/dt 打开。

在第一幅图像中、SHx 电压(如果 HS MOSFET 关断、该电压接近 HS 栅极至 GND 电压)下降时间约为40ns、这真的很快、可能很快。

第二幅图像可能显示了一些谐振、其振幅在开始时上升、然后缓慢下降。 找到谐振发生的位置会很有帮助。 使用接地弹簧钩时仅进行一次测量、应缩小发生谐振的区域。 近场探头也可能有用。 对于 MOSFET 开关后的振铃、100MHz 是相当正常的频率(高 di/dt、体二极管反向恢复)、但该谐振看起来不像。

1uS 的开关时间很长、我认为应该可以将其降低一点。

此致、

Grzegorz

您好、Grzegorz、

这是一个非常相似的设计。 我们对布局进行了一些大修、使其性能更好、现在我们不会一直看到芯片损坏。 我们还在整个 H 桥上添加了缓冲器、栅极电阻器、漏源极电容器、您当时的有用答案中通常会推荐这些内容。

我们使用 CSD19536KTT 作为 FET。

第一张图像有点过时。 我们栅极上的电容器太小、因此请使用第二幅图像作为上升和下降时间的参考。

我们必须等到新版本后再试用新的 MOSFET。 对于选择不受 dv/dt 导通影响的 FET、您会建议什么?

您好、Alcor、

我可以推荐 CSD18531Q5A,我在48V 和大约80ns 的上升/下降时间使用它们,没有 dv/dt 导通问题,但它是60V MOSFET,功耗比 CSD19536KTT 低。 如果我想快速开关 MOSFET、我会选择无引线封装、此外、为了限制 dv/dt 导通问题的风险、我会寻找具有可能高 CGS/CGD 比的 MOSFET、例如 CGD <<Cgs (Crss<<Ciss) and Qgd<Qg(th) or at least Qgd

如果 CSD19536KTT 确实遇到 dv/dt 导通问题、我会尝试在未来利用 DRV8353强下拉。 我会尝试避免使用栅极电阻器、使用可能的低值电阻器、例如10-15欧姆或使用与栅极电阻器并联的高速二极管(阳极连接到 MOSFET 栅极)。 如果不起作用、我将使用前面所述的参数尝试另一个2或3个 MOSFET 并比较波形。

以下使用 CSD19536KTT 的参考设计 可能对您有所帮助

https://www.ti.com/tool/TIDA-010056#technicaldocuments

对于更高的电流、我还将查看帖子

此致、

Grzegorz

您好 、Alcor 和 Grzegorz、

您发送的原理图看起来很好。 我唯一的建议是 SDO 和 nFAULT 的上拉电阻值较低(5k)。

您在 VM 上确实具有足够大的大容量电容。 我不确定 C55的额定值是多少、但47nF 很好。

我认为值得尝试一下 Grzegorz 建议的 FET。 它们的 Qgd 要低得多。 然后、您可以更详细地使用 IDRIVE 设置。

如果您决定坚持使用 FET、则可以使用较小的串联栅极电阻器、您使用的电阻器不会异常高、但我建议使用5欧姆左右的电阻器。

谢谢、

Michael

您好、Alcor、

感谢您发布上述波形。

我认为 LS 栅极信号的振铃可能是以下一种或多种原因造成的:

-在 HS MOSFET 导通期间由寄生电感和 di/dt 引起的振铃、包括 LS MOSFET 体二极管反向恢复、在 HS MOSFET 导通之前、HS 栅极电压会下降、这可能是由流经 LS MOSFET 体二极管的半桥的电流引起的。

-由上述由示波器探头拾取的现象引起的噪音

- dv/dt 导通

您能否回答以下问题作为开始:

-该半桥中是否有一个 LS 电流感应电阻器?

-您能不能告诉我们在获取这些波形时有什么电流从该相位流出?

-测量期间,您是否对所有探头使用了接地弹簧钩?

-什么是 VDRAIN 电压?

-是否可以在未连接负载的情况下进行相同的测量?

-您提到了 SOB 上的滤波器,它是在 SOB 输出之后还是在感应电阻器和 SPB/SNB 输入之间?

此致、

Grzegorz

嘿 、Alcor、

我刚刚注意 到、栅极上的电容器(C120、C127、C121、C128..ect)位于串联电阻器之前。 因此、来自器件的电流首先对这些器件进行充电、然后通过串联电阻器。 理想情况下、我们希望这些电容器直接放置在栅极和源极之间、并且两者之间没有电阻器。

我想回答 Grzegorz 的一些问题、但如果 Alcor 想要分享这些信息、这是他的决定因素。

至于布局、我已经向您发送了 DM。

谢谢、

Michael

您好、Alcor、

感谢您发布图表。

首先、我将对图本身以及我可以发现的栅极电路中的任何可能问题进行分析。

让我们看看"图19。 DRV8353S 的方框图+数据表中的图48和49"、SPX 引脚可能有两个功能、它们是电流感应放大器的正输入、可能也是栅极驱动器和 LS MOSFET 源之间的连接。 如果它们具有这两个功能、我不会在输入滤波器(R100、R101等)中使用电阻器。 我只保留大写。 C47、C84和 C85、但我会将它们尽可能靠近 DRV8353引脚放置。 我不会使用 COG 电容器、而是使用 X7R 类型、COG 类型具有良好的 Q 值、并且会增加该电路中任何谐振的风险。 介于100pF 和1nF (0603或0402)之间的值可能是正确的。 SPX 和 SNX 布线应作为差分对运行、如图所示、此外、我会将 LS MOSFET 栅极布线尽可能靠近 SPX 布线、这会降低栅极电路中的电感(如果 SPX 引脚在栅极驱动器和 LS MOSFET 源之间具有连接、 数据表中没有提到 CSA 输入滤波器、因此可能是这样)。

2.我同意 Michael 的意见、(C120、C127、C121、C128..ect)应直接放置在栅极和源极之间、尽可能靠近 MOSFET 端子。 但是、如果将这些电容器放置在电流位置有助于防止损坏 DRV8353、我会考虑使用小型高速肖特基二极管或单向 TVS 保护 DRV8353的 GLx 引脚、如 https://e2e.ti.com/support/motor-drivers-group/motor-drivers/f/motor-drivers-forum/966354/drv8353-problems-with-newer-batch-nr-ti98f-ti99f 或 /或通过 PCB 布局优化所述。 GLX 引脚面临的主要危险是负电压尖峰、与双向 TVS2、TVS4和 TVS7相比、单向 TVS 或肖特基二极管可能是更好的选择。

我想 TVS2-TVS7的作用是保护 MOSFET 栅极、但 CSD19536KTT 的栅极电压额定值为+/-20V、此外、它们具有非常大的 CGS 电容、如果不会损坏、我将首先重点保护 DRV8353端子。 查看 GHx 端子的绝对最大额定值、我认为它们比 GLx 更可靠、我将离开 TVS3、TVS5和 TVS6。

现在、让我们分析最后一个波形。 我的设计有点不同、它在没有 RC 缓冲器和交流电容器的情况下工作。 C86、C130和 C131、峰值电流高达25A、但我认为它应该没有太大不同。

乍一看、LS MOSFET 栅极上的振铃看起来像是由 di/dt 和寄生电感引起的振铃。 我想请您多做几次示波器测量、以更好地确保情况正确。 所有测量都应在接地弹簧钩、BW 滤波器关闭且探针设置为1:10的情况下完成(我们需要可能的高 BW)。 如果存在任何负/正尖峰、请调整视图以使其可见。

a 与之前相同的信号、但针对 LS MOSFET 源极、如果可能、如果您有电流探头(时基200-250ns)、还应增加 SHx 电压和相电流。

b 进行相同的测量、但在2-3个不同的相电流加上一个在负载断开时的相电流时、如果振铃振幅根据相电流值发生相应变化、这表明它主要是由 di/dt 而不是 dv/dt 引起的。

c 在与 a 点相同的条件下、检测电阻器上的单独电压(相对于检测电阻器的 GND 侧)。

此致、

Grzegorz

好消息、在这个电路板之后、我们已经在修订版中更改为单向 TVS 器件! 很高兴听到这个消息会有所帮助。

我们已移除所有滤波器、但如果您认为将电容器放回并靠近器件可能会起作用、我会尝试这样做。

我绝对会考虑您的布局建议!

我已经使用接地弹簧钩和1:10探针进行了测量、共振仍然在那里。 尽管如此、我们已经发现其中一些是接地波动、因为我们可以使用 探针测量示波器、并在整个电路板的不同接地端测量接地(这非常大、考虑所有不是该电机驱动器的外设总共长达10英寸) 并看到一些混乱。

非常感谢您的参与。 我没有其他问题要问、因此我将结束本主题、但你们都非常宝贵! 我确定我会在下一个修订版中再次回来、哈哈。