主题中讨论的其他器件: DRV8353、 MOTORWARE、 OPA835、 DRV8343-Q1

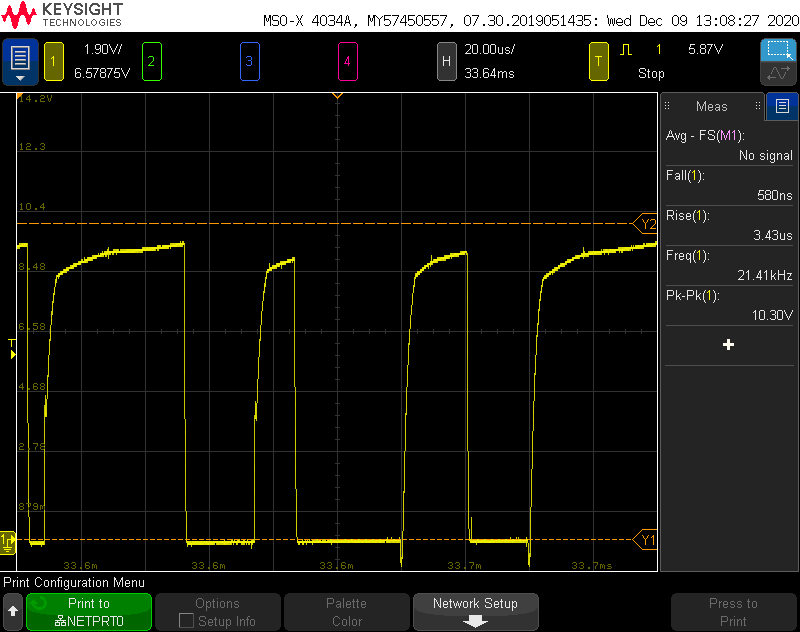

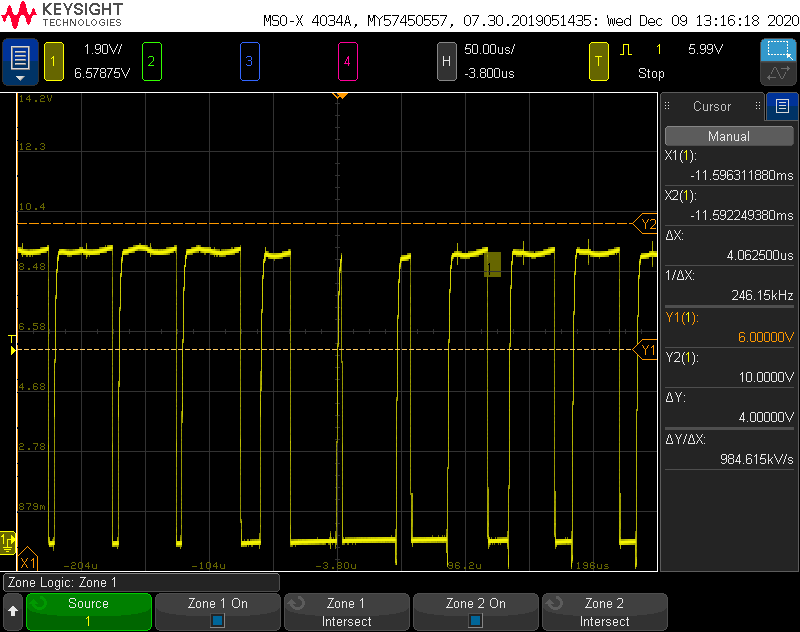

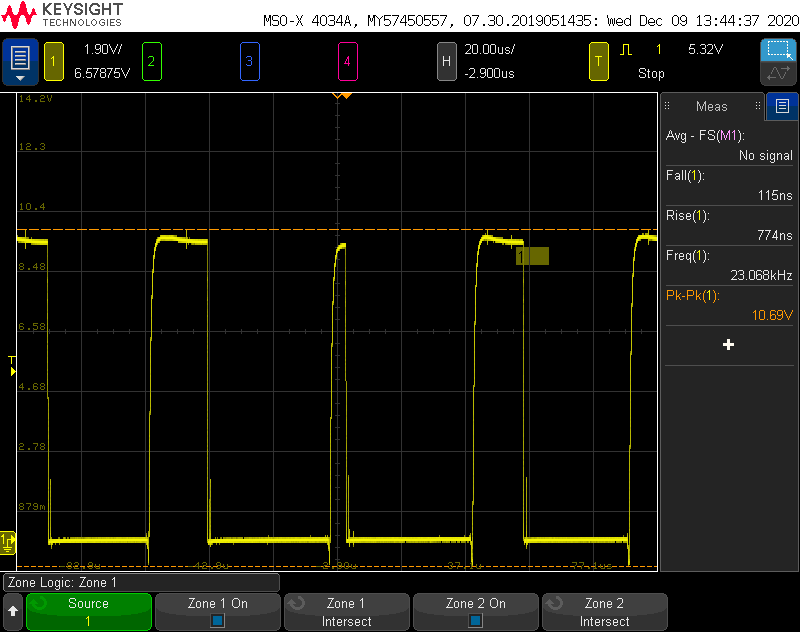

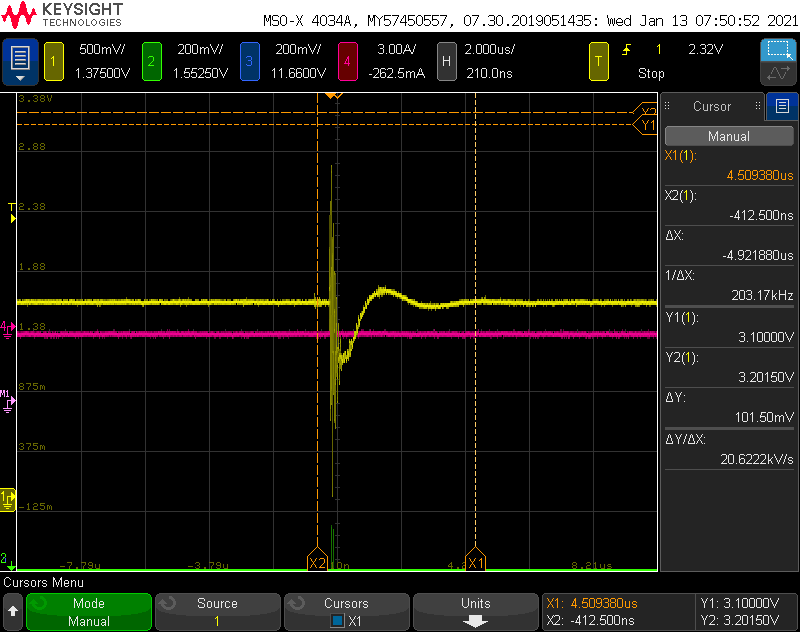

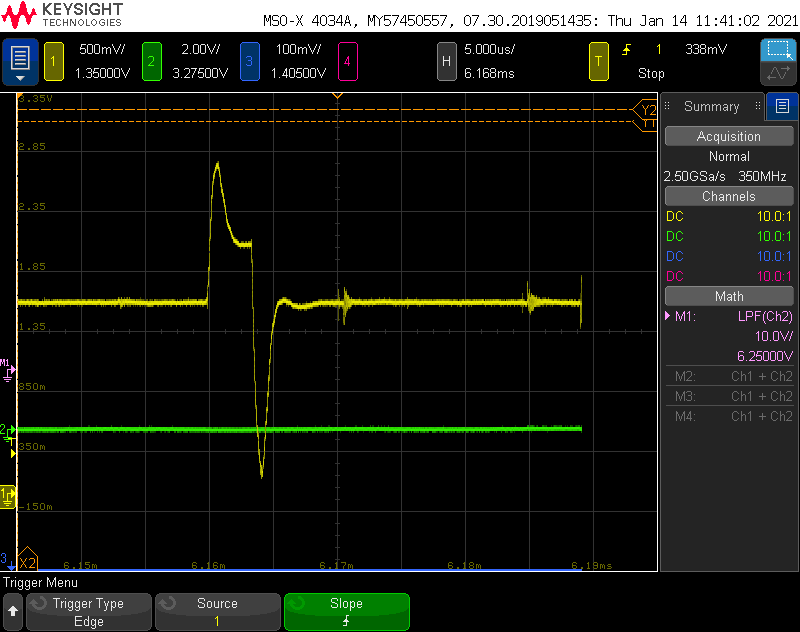

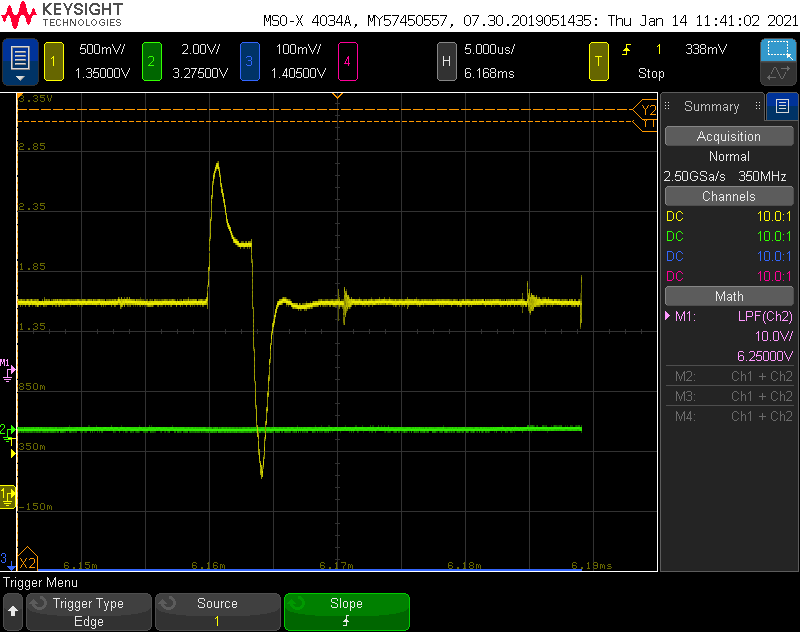

我们正在调试我们自己定制硬件的第一个版本。 我们主要复制了 DRV8353RS-EVM (电流滤波器、电压感应滤波器、VCP 电容器、CPH/CPL 电容器的值相同)。 我们发现一个问题、即当电机 RPM 在给定电压下达到最大电机 RPM 的90%左右时(发生在24V 至45V VM 的任何电压下)、我们开始在电机中抖动并开始失去控制。 如果我将电源上的电压增加几伏、抖动就会消失。 FET 栅极在这一点之前和之后都看起来很好。 电荷泵电压也看起来良好。

布局在6层上完成、几乎所有反馈信号都垂直于高电流路径运行、通常夹在缝合的接地层之间。 DRV8353布局已直接从 EVM 复制到。 这在空载电机上和低电流情况下发生。 我想知道其他人是否看到过此类问题、或者对故障排除的后续步骤有任何想法。

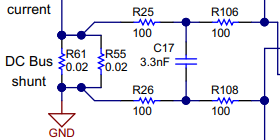

Rshunt = 2x 3m Ω 并联(1.5m Ω)@ 20增益(USER_ADC_FULL_SCALE_CURRENT_A=110A)

FET = 2个 IAUT300N10S5N015ATMA1 (共330nC Qg、2个并联)

IDRIVE (HS/LS)源= 1000mA

IDRIVE (HS/LS) 灌电流= 1800mA

USER_PWM_FREQ_kHz = 20kHz

USER_NUM_PWM_TICKS_PER_ISR_TICK = 1

USER_NUM_CTRL_TICKS_PER_SPEED_TICK = 20

USER_NUM_CTRL_TICKS_PER_TRAJ_TICK = 20

电动机 L = 280 μ H

电机 R = 0.2m Ω

电机极点= 3极对