尊敬的 TI 论坛:

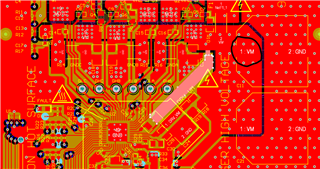

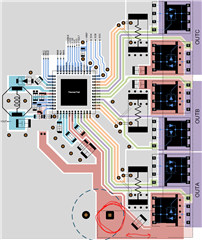

我们使用的是 DRV8353智能栅极驱动器。 我们遇到了 HS 和 LS MOSFET 开关问题、并优化了 idrive、tdead、tdrive 和 gate 电阻器。

我们使用的 MOSFET 具有100ns 的上升和下降时间以及45nC 的栅漏电荷和150nC 的总栅极电荷、这通常是如此。

当我们使用22 Ω 栅极电阻器时、 栅极和相位信号的过冲、下冲和振荡更少、但更重要 的是、HS 和 LS 开关不正确。

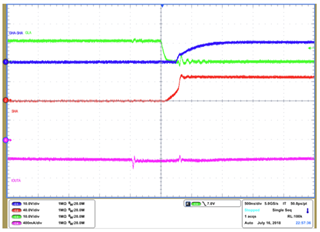

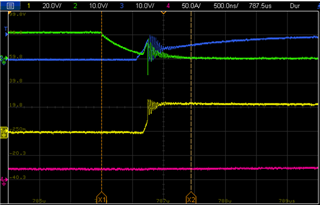

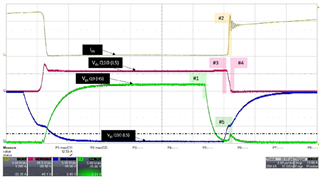

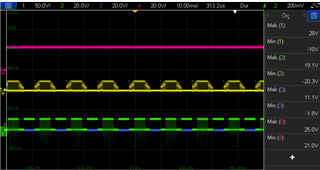

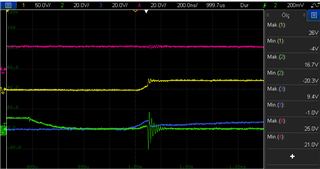

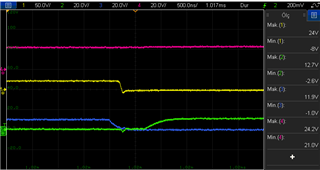

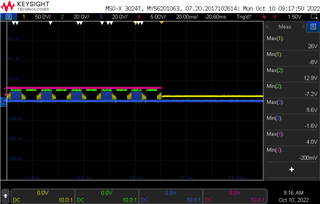

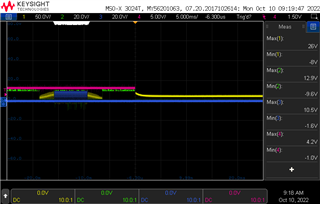

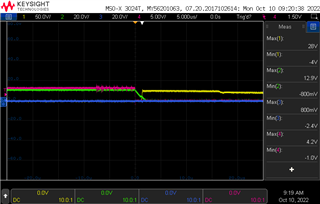

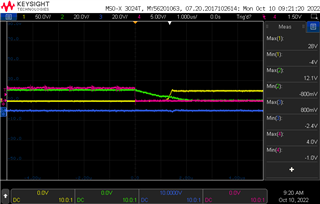

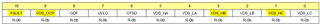

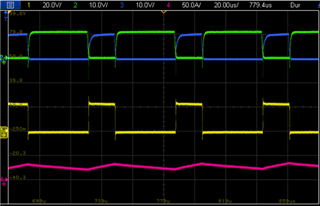

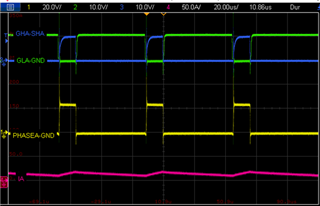

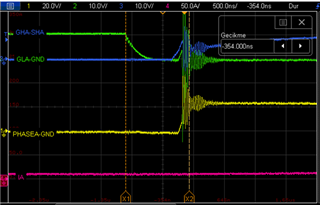

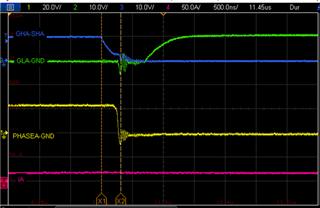

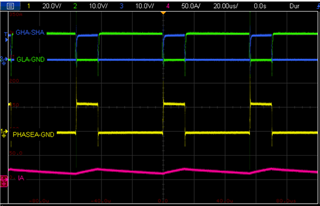

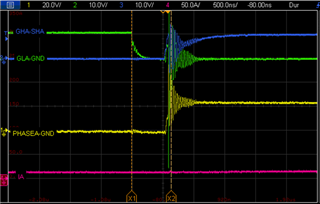

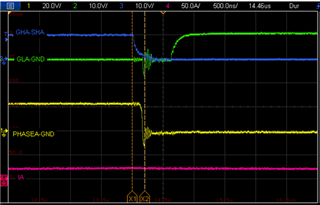

蓝色=GHA-SHA 信号、绿色=GLA-GND 信号、黄色=SHA-GND 信号、紫色= A 相电流

(Rgate = 22 Ω、 I_drives=300/600mA、t_deut=400ns、t_drive=4000ns、负载电流为20A)

由于栅极电阻器限制电流、在上升和下降时间内增加 I DRIVES 不会产生任何影响。

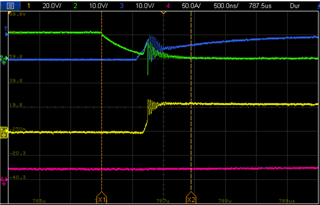

另外、如果我们将栅极电阻器值减小到2.7欧姆、则开关是正确的、但在开关的某个时间会发生振荡和其他有害的情况。

(R_GATE = 2.7 Ω、I_DRIVE = 300/600mA、t_dead = 400ns、t_drive = 4000 ns、 负载电流为20A)

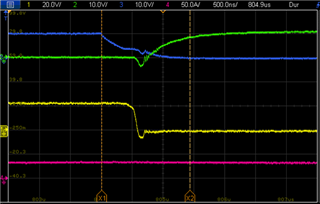

如果我们增大 I_drive 值、上升和下降时间会改变、但不必要的振荡会继续。

(R_GATE = 2.7欧姆、I_DRIVE = 1000/2000mA、t_dead = 400ns、t_drive = 4000ns、负载电流为20A)

- 22欧姆状态下的开关损耗大于2.7欧姆。 因此、MOSFET 上的热耗散非常大。 我们应该减小它。

- 如果我们突然将负载从20A 更改为5A 栅极故障、则在2.7欧姆栅极电阻器状态下会发生过流错误。 但是、当我们使用22欧姆栅极电阻器时没有误差。

- 为了减少相位电压过冲等、我们在 TI 应用手册《高功率电机驱动器应用的系统设计注意事项》中提出了一些建议。 由于 tdrive 和死区时间、可能会发生振荡。

您能帮我们解决这个问题吗? 我们如何克服这种信号混叠?

提前感谢。