您好!

我担心 VM 引脚的噪声是否会导致 IC 复位。

数据表显示、

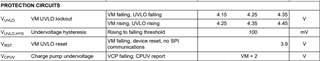

'当 VM 引脚上的电压降至 VM UVLO 复位电压(VRST、最大值3.9V)以下时、SPI

通信不可用、数字内核关断、FAULT 和 UVLO 位为低电平、nFAULT 引脚为高电平。'

如果 VM 电压保持在 VRST 以下、复位需要多长时间?

我找不到数据表的描述。

请告诉我。 此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我担心 VM 引脚的噪声是否会导致 IC 复位。

数据表显示、

'当 VM 引脚上的电压降至 VM UVLO 复位电压(VRST、最大值3.9V)以下时、SPI

通信不可用、数字内核关断、FAULT 和 UVLO 位为低电平、nFAULT 引脚为高电平。'

如果 VM 电压保持在 VRST 以下、复位需要多长时间?

我找不到数据表的描述。

请告诉我。 此致、

嗨、Fumika-San、

我在数据表中也找不到这些确切的信息。 UVLO 的值范围从最小4.15V 到最大4.35V (典型值4.25V)不等、因此我确信该范围也是影响其跳变时间的因素。

让我向我们的设计团队询问这些信息。 通常需要3-5天的时间来响应 FYI。

同时、我可以向您保证、VM 引脚上导致 IC 复位的噪声对于该器件不是常见问题、只要您遵循建议的布局、大容量电容器和 VM 范围、我相信您将遇到 UVLO。

此致、

Jacob