各位专家:

客户在 ESC 中使用 DRV8301DCA、需要确保 ESC 在启动时不会接合电机、并要求他进行安全超控、以确保在不必要时不会意外控制。

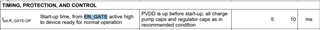

他认为他可以使用 EN_GATE 引脚作为该控制。 如果芯片被无限期保持在低电平(几分钟到几小时)、它会发生什么情况? 这是否会造成任何形式的损坏? 一旦他再次将 EN_GATE 驱动为高电平、8301是否会返回到运行状态、或者此时是否需要 POR?

让我重申一下:

1) "如果芯片无限期保持低电平(几分钟到几小时)、会发生什么情况?"

2) "这是否会造成任何形式的损坏?"

3) "一旦我再次将 EN_GATE 驱动为高电平、8301是否会返回运行状态、或者此时是否需要 POR?"

4) "此外、将 EN_GATE 保持在低电平是否会关断降压转换器或以任何方式对其产生影响?"

我们希望收到您的确认/建议。 谢谢你。

此致、

Gerald