大家好、我目前正在尝试通过 SPI 为 Sitara-AM437x 处理器设置 DRV8462evm。 启动后、我发送5个我要写入的寄存器、即0x4、0x5、0x6、0xC 和0x10、 如下所示。 尽管 MOSI 上的传出数据包是准确的、但我没有从驱动程序获得响应。 我连接了板载 EVM 微控制器、并在通过 TI GUI 控制驱动器时查看了 SPI 事务、发现我的 MISO 线路在事务之间拉低、而板载微控制器将线路拉高。

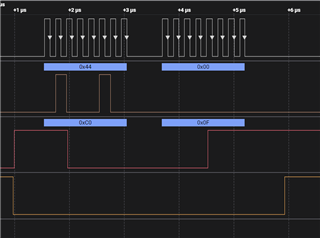

我的 SPI 事务:

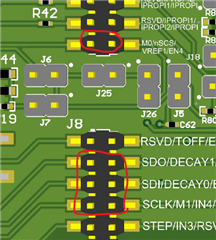

特写:

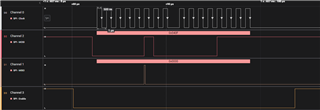

用于参考的板载 MCU 事务:

我的 MODE 引脚也被上拉至逻辑高电平、以便在 SPI 模式下使用驱动器。 我提供24V 电压、因为 VM 和 TP28显示为驱动器本身提供5V 电压。

我已经尝试过的内容:

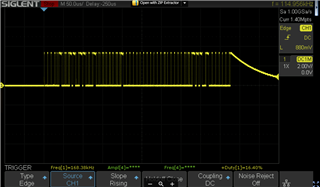

MISO 线路的内部上拉电阻(3.3V)-一旦 CS 被拉至低电平、信号就被拉至0v。

MISO 线路的外部上拉电阻(3.3V、3.9kΩ Ω)-线路在整个传输过程中从未被拉低并保持逻辑高电平。

在启动 SPI 事务之前、nSleep 脉冲介于20us 和40us 之间。 交易期间无变化。

切换 MISO 和 MOSI 线路以确保正确连接信号。

如果我不知道还有什么要尝试、我们将感谢您的任何帮助。

另外、数据表指出:"器件 SDO 上的数据在 SCLK 的上升沿进行传播、而器件在 SCLK 的后续下降沿捕获 SDI 上的数据。" 我从未遇到过在时钟的不同边缘发送和接收数据的器件、即 SPI 的 CPHA。 由于我只能在时钟的一个边沿上发送和接收数据、因此应该如何在微控制器端处理此问题。