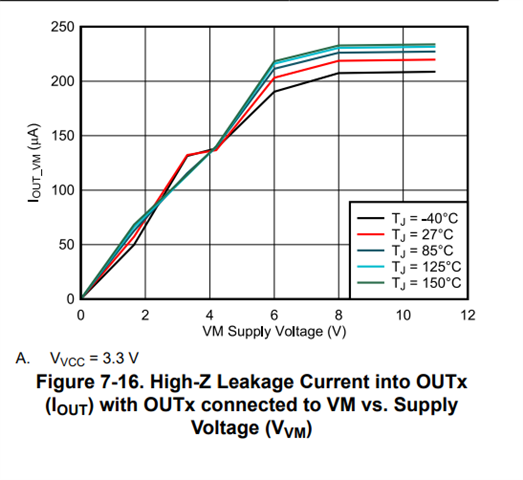

我设计了一个实现 DRV8210DSGR 的器件、并且看到的泄漏电流比我想的要大。 数据表指出、在将输出连接到 VM 时、在高阻态模式下会出现一些泄漏、但不太清楚预期是什么。 我的测量结果表明、泄漏完全取决于 OUTx 引脚电压、并且似乎与 VM 完全无关。 也就是说、无论 VM 设置为什么、将电桥置于高阻态模式并向输出引脚施加电压都会产生大约等于20-30k 下拉电阻的泄漏电流。 数据表与此并不矛盾、但也不清楚泄漏是什么。

这是预期的功能、还是我的实施中可能存在缺陷? 该实现方案在其中一个输出上具有100K 至3.3V 和100K 接地的电阻分压器、以便即使在 H 桥禁用时也能将输出保持在可测量区域内。 而不是放在1.65V、输出变为0.8左右。 在这种情况下、这不是一个大问题、但也不是最佳问题。 是否可以减少或以某种方式避免泄漏?