大家好、

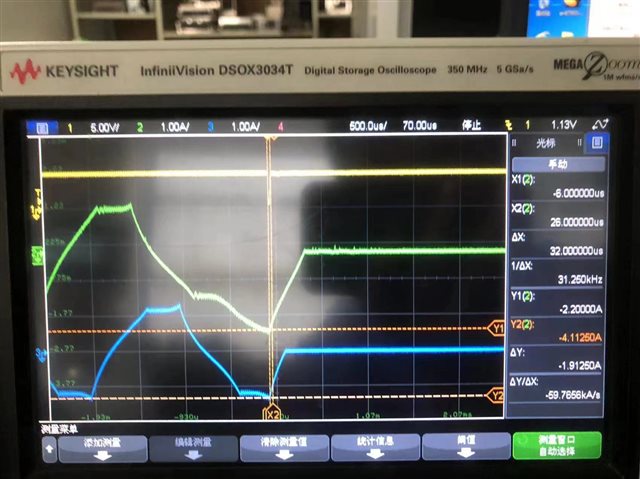

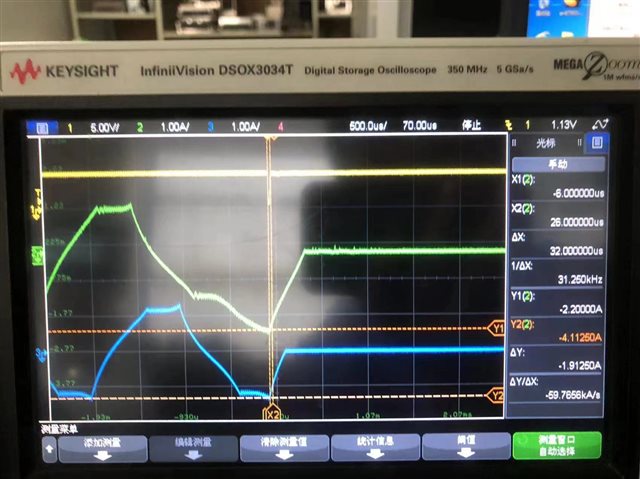

客户捕获了一个奇怪的波形、如下所示。 CH1是故障、CH2是相电流、CH3是 B 相电流。 当 A 相电流超过 OCP 阈值(1.8A 最小值)时、FAULT 引脚被拉至低电平。 奇怪的是、FAULT 引脚后来被上拉。 如您所知、在应用 nRESET 引脚、nSLEEP 低电平和高电平切换或移除并重新应用 vmx 之前、器件将保持禁用状态。 在上述测试中、未发生这3种条件、但 FAULT 被上拉。 您能解释一下吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

客户捕获了一个奇怪的波形、如下所示。 CH1是故障、CH2是相电流、CH3是 B 相电流。 当 A 相电流超过 OCP 阈值(1.8A 最小值)时、FAULT 引脚被拉至低电平。 奇怪的是、FAULT 引脚后来被上拉。 如您所知、在应用 nRESET 引脚、nSLEEP 低电平和高电平切换或移除并重新应用 vmx 之前、器件将保持禁用状态。 在上述测试中、未发生这3种条件、但 FAULT 被上拉。 您能解释一下吗?

您好、 Naizeng、

感谢您联系我们。 您提到 A 相电流超过了 OCP 阈值。 A 相电流是多少? 我无法通过示波器捕获准确测量它。 时间/div 设置为500us、请确认。 这是否仅通过一个器件、客户 PCB 或 DRV8824EVM 实现? 您是否能够交换绕组连接并获得另一个捕获、从而看到 B 相电流的行为相同。 为什么 A 相电流与示波器捕获中的 B 相相比峰峰值更高? 您能否分享一下驱动器原理图?

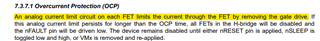

请注意、在此器件中、每个输出都有独立的电流限制电路、考虑 VDS 而与检测电阻无关。 因此、一个 FET 可以 根据其 VDS 压降进行电流限制。 可能这是客户观察到的情况。 但我们需要验证以确认发生了什么。

此致、Murugavel