我的设计会在 GHx 上产生相对于 SHx 的短负瞬态、该瞬态超过数据表中的绝对最大值(-0.3V)。 我知道此额定值是为了保护齐纳二极管、但 无法找到有关此二极管可靠吸收多少能量的任何信息、 或有关此二极管和栅极驱动 FET 体二极管的电容和反向恢复并联的任何东西、以判断它是否导通。 您能提供更多细节吗?

更一般地说、我不明白使用 此栅极驱动器的任何合理设计如何 避免超过 -0.3V 规格。 状态机仅在关断第一个可灌入100 mA 的 FET 时应用 I_HOLD (在 SHx 以下是否也适用?)。 如果一个外部 FET 通过100 mA (最小设置)的任何东西关断、看起来该齐纳二极管或栅极驱动 FET 的体二极管必须导通。 在 米勒平坦区域期间(在关断期间发生、取决于电流流入/流出半桥的方向)、被关断的外部 FET 的栅极有100 mA 从其流出的外部 FET 的 C_gd 流出。 这 意味着将另一个外部 FET 的 V_GS 保持在0V、需要从其 C_gd 中拉取相同大小的电流、如果外部 FET 相同、则电流大小也相同。 I_HOLD 不足以灌入足够的电流来将其保持在0V、因此必须导通其他器件。 (实际上 C_gd 随 V_DS 而变化、因此在 V_DS 转换结束时更糟糕。)

我看到了关于这个问题的其他几个主题、但我不确定如何处理、因为这些主题似乎都没有陈述可以实现的安全最大额定值。

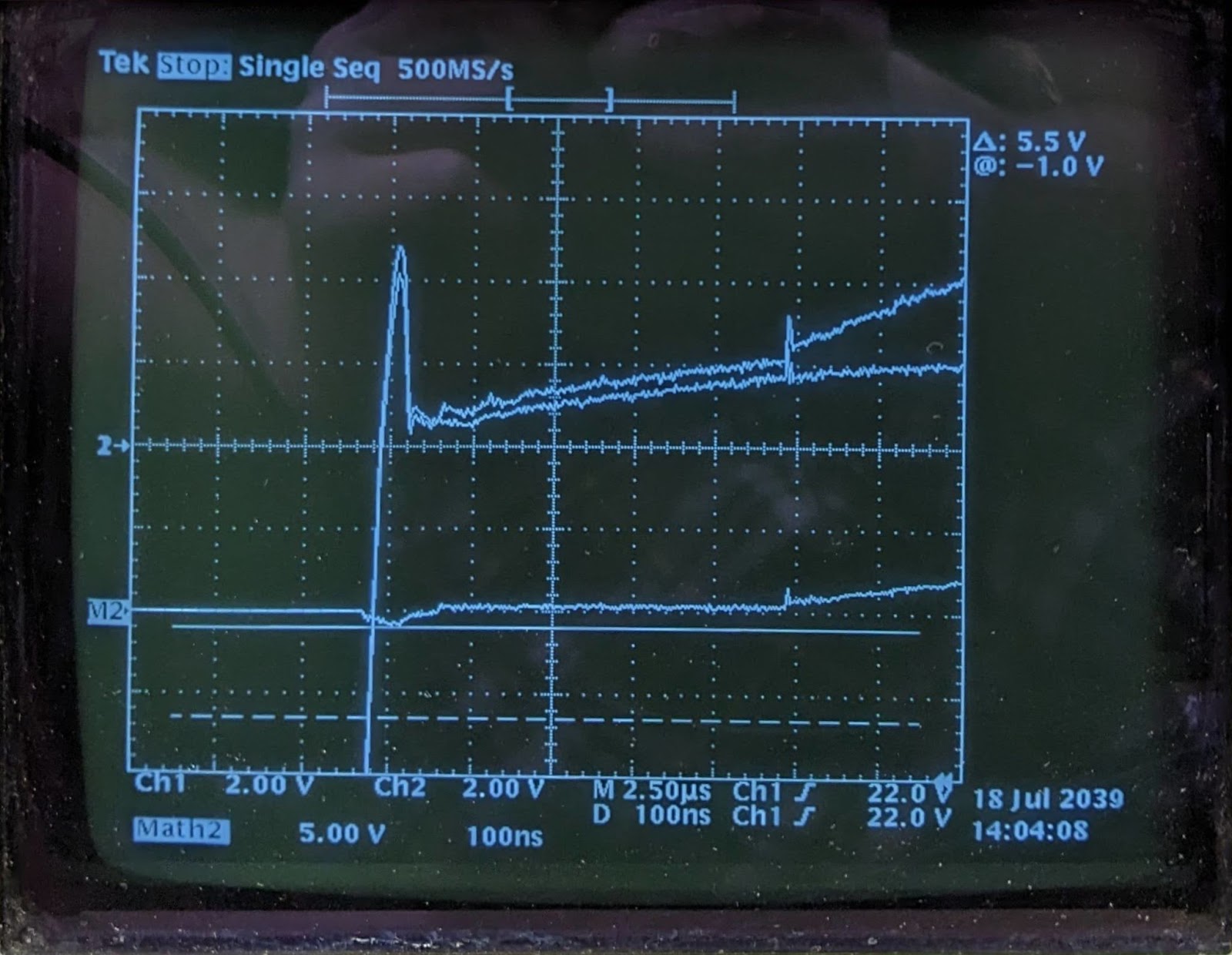

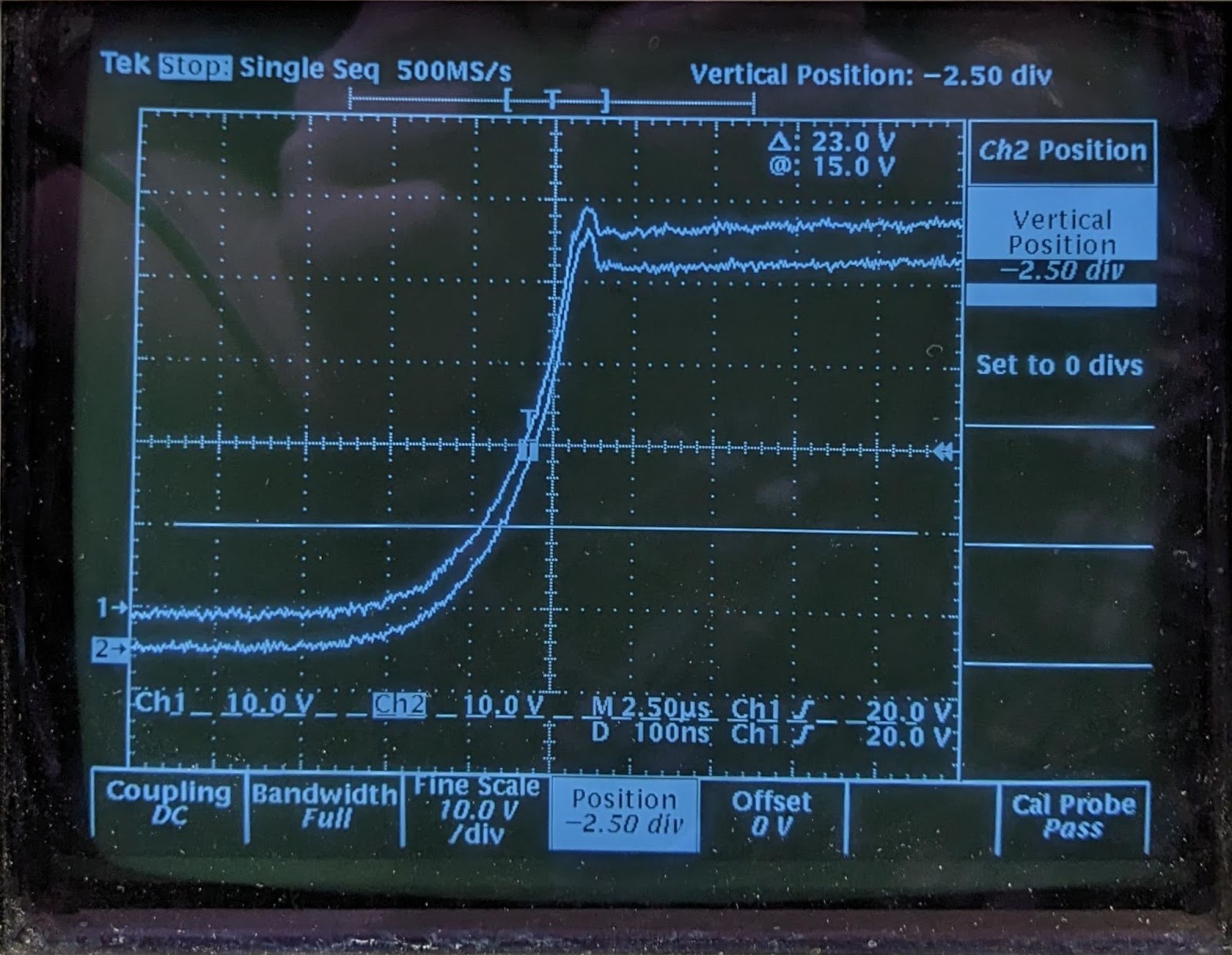

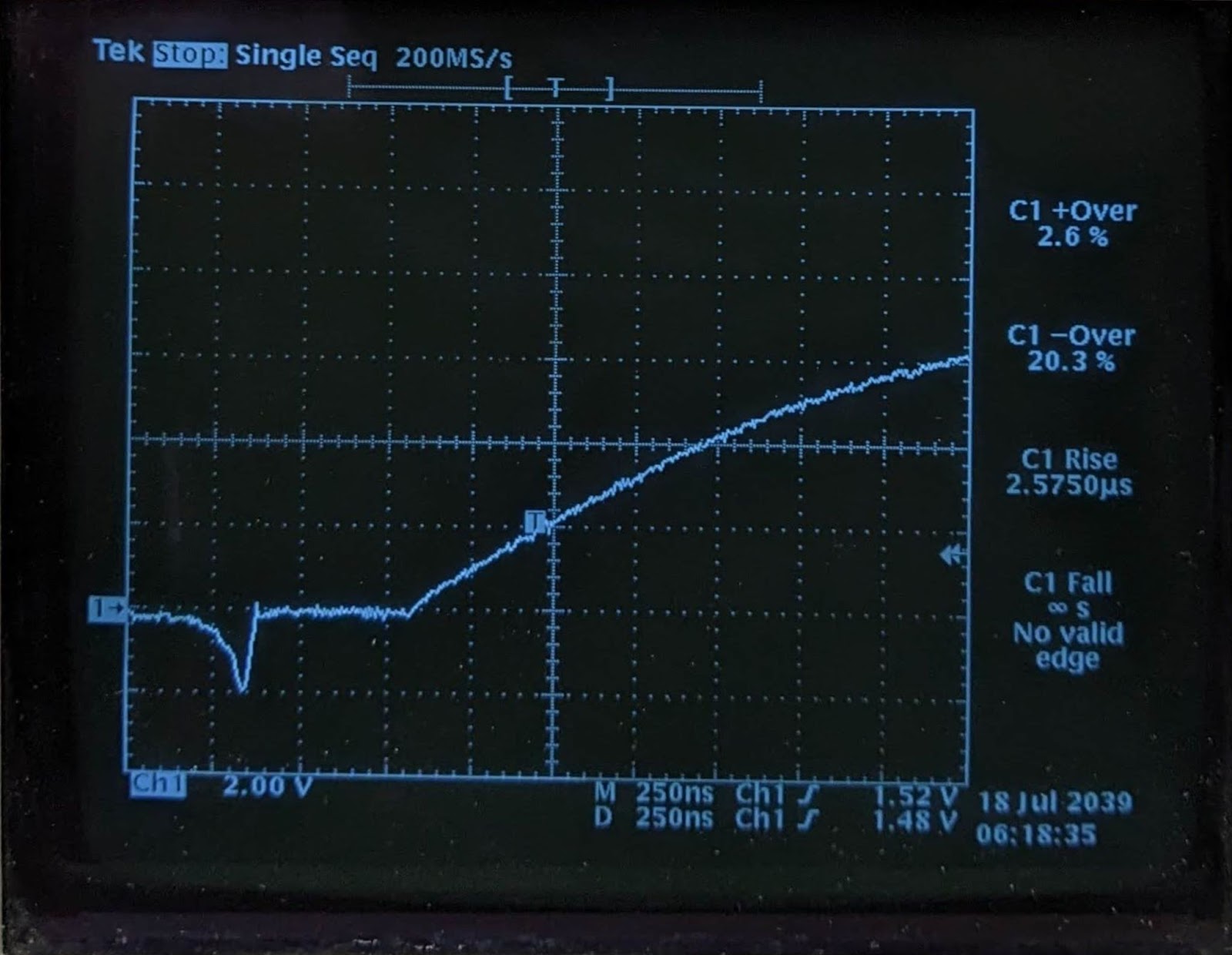

以下是 栅极驱动器附近的电压示例(GHx 相对于 SHx、带接地弹簧的单端无源探头、受测器件依靠电池电源悬空、500 MHz 示波器和探头):

这是针对300 mA IDRIVE (全部4个)、它足够慢、可以在它打开第二个 FET 时刚好达到 TDRIVE。 我想增加电流以加快开关速度、但这往往会进一步超过绝对最大额定值、因此我不确定这是否会造成损坏。

我的设计使用2个 并联的 IPTG014N10NM5 (全部3相共12个 MOSFET)。 对于每个单独的 FET 栅极、我都有一个1欧姆的栅极电阻器。 这个例子是300A 电流流入相关的半桥、因此低侧 FET 的关断会向高侧 FET 的体二极管进行换向。