背景:

- 我是一家协作机器人公司的一名设计工程师、该公司广泛使用 TI 产品。

- 然而,我面对的是一个严重的问题,详见下文,我希望能在时间紧迫的情况下,迅速作出回应,协助我处理此事。

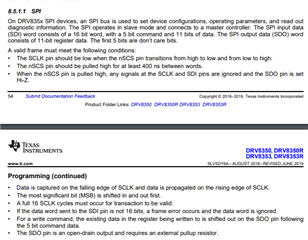

- 相关的 SPI 总线用于与三个从器件进行交互、这三个从器件分别是两个 H 桥驱动器(DRV8350:数据表)和电机轴上的编码器(ICMU150)。 主站为 STM32H730IBT6。

- 编码器位于单独的 PCB 上、两个栅极驱动器位于主器件周围的单独 PCB 上。

- SPI 总线通过线束路由到编码器、而到栅极驱动器的路由是通过板对板连接器。

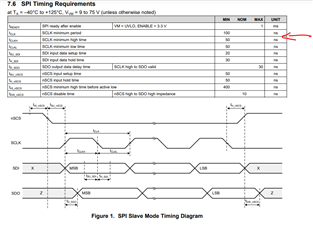

- 时钟在总线空闲状态期间配置为低电平。

- 未选择从器件时、nCS 为高电平。

- 如果所述的从器件未被选择、则编码器的从器件输出(SDO)为高阻态。

- 未选择时、两个栅极驱动器的 SDO 会被拉高至5V

可在此处找到该原理图: 原理图

问题:

- 当线束连接到编码器时、会从栅极驱动器输出错误的值。 图像:附件 A

- 此外、在总线空闲状态期间、时钟和 MOSI 线路看起来为~2V。

- 我最初的怀疑是电容、但时钟和 MOSI 线路始终不会从2V 电平放电。

- 当编码器的 SPI CLK 断开时、正确的寄存器值会在时钟沿从栅极驱动器输出。

- 此外、在总线空闲状态下、时钟接地。

- 请参阅 IMG:附件 B