主题中讨论的其他器件: DRV8706-Q1

您好!

我将在以下原理图中使用 DRV8701芯片-

e2e.ti.com/.../DC-Driver-_2300_1-Pololu-.pdf

在连接器 A13上、我要连接一个直流电机。

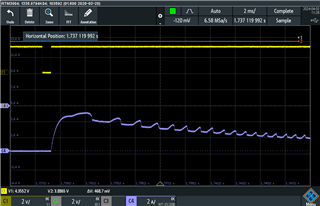

我有问题、当我使用电机时、我的 nFault 将变为低电平。 我想充分理解为什么会发生这种情况。

这是输出电流和 nFault 引脚-

黄色表示故障

蓝色表示电机的电流

我可以看到它在电机消耗电流之前发生。 我希望了解为什么会发生这种情况以及如何解决这种情况。

谢谢!

迈克尔