大家好!

我们正在使用 drv8308开发该项目。

我将测试我设计的电路板。

电机运行良好、但读取电机寄存器可确认 CP 故障。

VCP (28)和 VM (27)之间的1uf-25V 电容器

将电容器更改为1uf-50v 是否解决了该问题?

我想尝试更改这个电容器、但没有1uf-50v。

在测量 VCP 电压时、测量34.4V。

是否有办法修复 CP 故障?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Shshin:

CP1和 CP2之间的电容器的电容和电压是多少?

Unknown 说:VCP (28)和 VM (27)之间的1uf-25V 电容器

将电容器更改为1uf-50v 是否解决了该问题?

我们建议使用额定电压大于或等于35V 的 VCP-VM 电容器。 使用额定电压低于35V 的电容器可能会由于陶瓷电容器降额而导致电容降低。

如果您尚未 清除、器件上电后是否可以手动清除 CPFAIL 位? 另外、如果在电机运行时清除了 CPFAIL 位、能否检查 CPFAIL 位是否再次有效?

此致、

约书亚

你好,Joshua。

我在下面写下了您的问题的答案。

Q1: CP1和 CP2之间的电容器的电容和电压是多少?

=>连接到 CP1和 CP2的电容器是0.1uf-50V

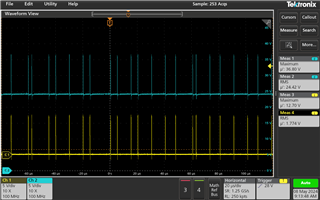

它是电机运行时 CP1和 CP2的波形。

CP1:黄色、CP2:蓝色

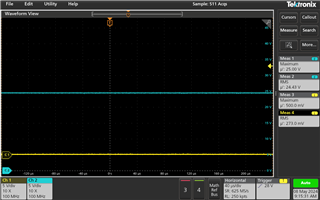

它是电机未运行时 CP1和 CP2的波形。

CP1:黄色、CP2:蓝色

Q2: 如果您尚未启用 CPFAIL 位,那么在设备上电后是否可以手动清除 CPFAIL 位? 另外、如果在电机运行时清除了 CPFAIL 位、能否检查 CPFAIL 位是否再次有效?

=> 给电路板加电后、CPFAIL 位是0。 当电机运行时、CPFAIL 位为1。

如果 我在电机运行时手动将 CPFAIL 位更改为0、则 cpfail 位保持为0。

没有1uf-50v 电容器。 购买需要一些时间。 但是、在购买之前、我希望确保问题得到解决。

Ragards,

申

你好、

从捕获来看、似乎器件 正在作为 待机或睡眠模式的输出或上电。 如果 ENABLE 位设置为非活动状态、则 将禁用 VCP 和 VREG。 当 VREG 和 VCP 被禁用时、VCP 将是~VM 电压、而 VREG 将是~0V。 您能否检查使能和/或复位引脚是否在接近 VCP 开始上升时的状态变化? 如果这些引脚在器件退出或进入睡眠模式时改变状态、则会 禁用/重新启用 VCP、从而导致 CPFAIL 重新 置位。

如果使能和复位引脚未改变状态、您能否提供对 U 处 VCP、VREG、ENABLE 和相电流的捕获 、包括器件上电时的启动情况、包括旋转电机、停止电机和再次旋转电机?

此致、

约书亚

你好、Joshua、

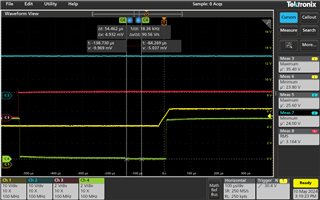

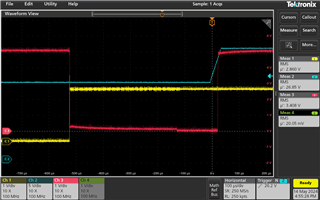

蓝色: VM ,红色: ENABLE ,黄色: VCP,绿色: FAULTn

当电机运行时、FAULTn 信号变为高电平->低电平->高电平、这是否正常?

该问题的含义是、当一切正常时、FAULTn 信号是否保持 Hgih 状态?

FAULTn 信号为什么再次变为高电平?

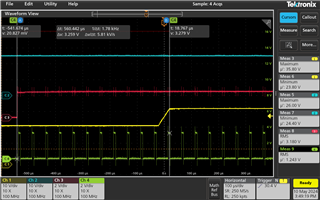

蓝色:VM,红色:ENABLE,黄色:VCP,绿色:CLKIN

Cpfail 是否会因为使能信号变为低电平->高电平时 SCLK 信号直接进入而发生?

如果 CLKIN 中没有 PWM 输入且使能信号输入为低电平->高电平、VCP 电压是否会升高?

你好、

FAULTn 信号在电机运行时变为高电平->低电平->高电平,这是正常吗?

如果在电机旋转时发生这种情况、并且未向使能端提供低电平->高电平或高电平->低电平信号、则表示存在问题、请提供所报告的故障。 如果该问题与捕获相关 、请参阅我对下一个问题的评论。

为什么 FAULTn 信号再次变为高电平?

我看到使能位为低电平、然后在捕获开始位置附近变为高电平。 当 ENABLE 为低电平时、如果所有模拟电路(包括电荷泵(VCP))都被禁用、器件将处于低功耗状态(请参阅数据表的第7.3.3节)。 当 ENABLE 设置回高电平时、DRV8308通过一个唤醒例程、最长需要1ms (请见数据表的第6.6节)。 在此唤醒期间 、虽然在唤醒序列中的 VCP 之前将 FAULTn 唤醒、但会将模拟电路重新开启、这会导致由于 VCP 低于 CPFAIL 阈值而导致 FAULTn 引脚被拉低。 当 VCP 引脚唤醒时、由于 VCP 电压现在高于 CPFAIL 阈值、FAULTn 引脚将被拉高。

如果 CLKIN 中没有 PWM 输入且输入使能信号为低电平->高电平,VCP 电压是否升高?

是的、即使在 ENABLE 设置为低电平至高电平时没有 PWM 输入、VCP 电压也会上升。

如果启用信号变为低电平->高电平时 SCLK 信号直接进入,是否会发生故障?

我们希望、只要向使能引脚提供一个低->高信号、就会发生 CPFAIL。 当提供使能时,一个低信号 VCP 应从>VM+3V 转到 ~VM。

此致、

约书亚

你好,Joshua。

红色: FAULTn,黄色: ENABLE ,蓝色: VCP

通过该波形可以看出、当 ENABLE 变为低电平->高电平时、FALTn 信号输出为高电平->低电平

因为 VCP 早于 VM +3V 电压。

VCP 电压上升后、FAULTn 信号变为低电平->高电平。

CPFail 位目前未自动变为1 -> 0是否正确?

用户是否应该直接将 Cpfail 位设置为0?

是否有任何方法可以快速提高 VCP 电压?

我认为、CPFAil 肯定会出现在我测试的电路板上、

是否有办法防止 CPFAIL 发生?

当使能信号变为低电平->高电平时、测量 HSU 侧的信号是否有帮助?

星期三是我休息的日子。

我将在周四进行测试。

请回复。

感谢您的帮助。

此致、

申

你好、

CPFail 位目前未自动变为1 -> 0是否正确?

用户是否应该直接将 Cpfail 位设置为0?

[/报价]正确、CPFAIL 位不会自动从1->0改变。 在用户将0b 写入 CPFAIL 位之前、CPFAIL 将保持设置为1b。 将 ENABLE 从 LOW 设置为 HIGH 并等待1ms 后、可以将 CPFAIL 位设置为0b 以清除故障。 如果再次设置 CPFAIL 位且 ENABLE 位未从 LOW 变为 HIGH、则可能会出现问题。

是否有任何方法可以快速提高 VCP 电压? [/报价]使能引脚拉高后 VCP 电压上升的时间无法更改。 由于生产差异、该时间会因器件而异、但我们预计 VCP 会在1ms 的唤醒时间之前上升。

[/quote]是否有办法防止 CPFAIL 发生?当 ENABLE 从低电平变为高电平时、无法阻止 CPFAIL。 当 ENABLE 从低电平变为高电平时、预计会发生 CPFAIL。

此致、

约书亚

[/quote][/quote]