大家好、

是什么在内部推动了该要求?当 VDD 断开连接时、将这些引脚拉至1.8V 有什么影响?

谢谢!

卡梅伦

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

感谢悉尼、

I2C 电压电平为1.8V 或3.3V。 很可能为1.8V

我正在使用评估电路板、VDD = GND、而 SDA/SCL = 1.8V、我没有看到问题。 但是、如果不了解内部情况、我会不愿意给最后一个大拇指

谢谢!

卡梅伦

您好、Cameron、

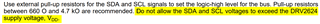

否、我们没有这方面的最大电流规格。 让 SDA 和 SCL 的电压高于 VDD 不会立即损坏器件、但如果始终如此、则会在长期内损坏器件、因此我们建议不要这样做。 如果有一个规范可以 安全地解决这个问题、 我们建议这样做。

我首先应该问一下您为什么要在 SDA 和 SCL 打开时将 VDD 调为0V? 我假设在不使用器件时将其关断、 以避免拉取不必要的电流、但 I2C 线路需要保持激活状态以控制其他器件、对吗? 如果是、这就是 NRST 引脚的用途。 仍需要向器件提供 VDD、但 NRST 引脚会将器件置于关断状态-仅消耗 nA 级电流! 它会关闭器件内的所有模块、甚至是 I2C 通信。 如果我对申请有误解、请更正。

具有更大的 VDD 将允许您在输出上获得更大的电压、因此 它将提供更强的振动、但不一定具有"清晰"的感觉。 通过集成自动超速驱动和自动制动功能、实现更逼真的感觉。

此致、

悉尼诺斯卡特

我应首先问一下您为什么要在 SDA 和 SCL 打开时将 VDD 调为0V?

我误解了使用案例、我可以澄清… 当 SDA/SCL = 1.8V 时、用例为 VDD = 5V

[/报价]

- 保持 NRST 为低电平可以消除该问题? 也就是说、如果我们在 VDD = 0V 时一直保持 NRST 为低电平、而 SDA/SCL 为1.8/3.3V 时、这是个问题吗?

您是否愿意对此进行评论? 我理解是的、这是一个问题