您好!

如前一篇文章 https://e2e.ti.com/support/motor-drivers-group/motor-drivers/f/motor-drivers-forum/1068138/drv8353-dc-offset-variations-problem 所述、 我们的设计中似乎存在相同或类似的问题。 然而,当我读到那篇文章时,我觉得,真正的根本原因没有真正找到。

我们的电路板具有4个驱动器电路(SPI 型号、DRV8353SRTAR)、每个电路都具有3个放大器(总共12个放大器)。 在每个电路板上、其中一个或两个存在这种直流变化问题。 存在问题的不同电路板之间的输出不同。

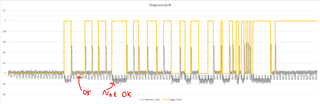

运行校准例程后、可以通过寄存器中的 CAL_MODE 设置或通过切换 ENABLE 引脚来执行校准例程、似乎校准例程将在两个不同结果中的一个结果中结束、并且非常随机、最终会产生这种结果。 在下图中、在黄色信号的每个侧面触发自动校准功能(CAL_MODE 位在100ms 内设置为1、然后设置为0)。 灰色信号对应于我们测量的电流信号。 PWM 输入始终被禁用(低电平)。 该电路的其他两个放大器按预期运行、会在每次校准过程后产生相同的失调电压。

校准后、电流测量几乎按照预期工作。 它具有正确的增益等、但该小偏移始终存在(直到执行下一个校准过程)。

每次运行之间校准不同的原因有任何疑问吗? 或者这是否在预料之中? 我们在校准后可以预期的放大器输入失调电压是多少? "故障"偏移对应于放大器输入端大约0.5-1mV 的电压。 在本例中、校准例程是否具有切换的某种"离散步骤"?

此致、

丹