主题中讨论的其他器件: DRV8837、 DRV8262

工具与软件:

您好!

根据数据表、输出引脚额定电压为-VSD~VM+VSD。 由于 VM 计划在6.5V 电压下使用、因此输出引脚的额定电压为-1.0V 至7.5V。

[问题]

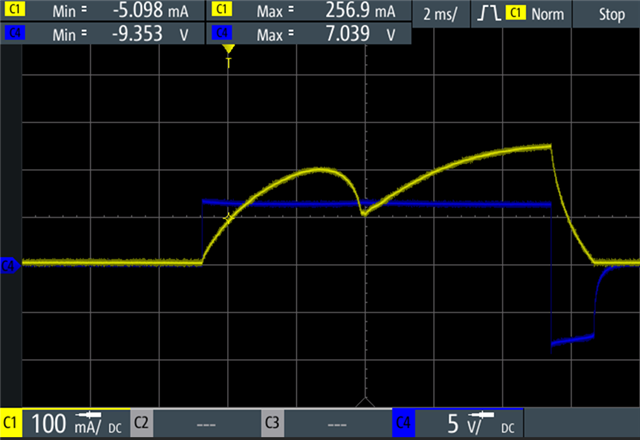

由于 DRV8212P 不执行衰减控制、因此反电动势将导致电压超过额定值、如下面的波形所示。

-蓝色:螺线管施加的电压(OUT1至 OUT2 )

-黄色:电磁阀电流(OUT1)

DRV8212P 是否需要衰减控制? 是否有其他对策?

谢谢!

Conor

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

根据数据表、输出引脚额定电压为-VSD~VM+VSD。 由于 VM 计划在6.5V 电压下使用、因此输出引脚的额定电压为-1.0V 至7.5V。

[问题]

由于 DRV8212P 不执行衰减控制、因此反电动势将导致电压超过额定值、如下面的波形所示。

-蓝色:螺线管施加的电压(OUT1至 OUT2 )

-黄色:电磁阀电流(OUT1)

DRV8212P 是否需要衰减控制? 是否有其他对策?

谢谢!

Conor

嗨、Conor、

哇、这是一个很大的负电流、肯定会损坏器件。 您可能需要大容量电容、甚至需要一个反向保护二极管、以帮助防止该浪涌。

本文档可能会帮助您: 使用 DRV 驱动螺线管(修订版 A)(TI.com)

此致!

Jacob

尊敬的 Jacob:

感谢您的答复。 您可能误解了、因为我的解释令人困惑。

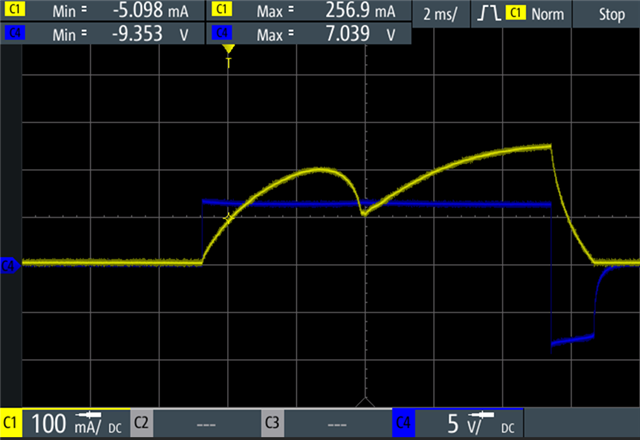

先前的波形是 OUT1和 OUT2之间的电压、因此我现在已经获得 OUTx 和 GND 之间的电压波形。

我特别担心由于反电动势、最大输出电压约为7.9V。 这似乎超过额定的 VM+VSD (=6.5V+1V)。

・紫色:OUT1-GND 电压

・蓝色:Out1电流

・黄色:OUT2-GND 电压

■电磁阀:打开

■电磁阀:关闭

此外、Vout 额定值定义为"-VSD to VM+VSD"、但 DRV8837等较旧的产品没有这种描述。

如果您了解添加此 Vout 额定值的背景知识、敬请告知。

谢谢!

Conor

嗨、Conor、

Hmm 您能否在波形期间同时捕获 VM-GND 电压? 我想您会发现、由于 VM 电压在 OUTx 上升的同时上升、VM 和 OUTx 之间的差值随时都将处于规格范围内。 这是一种很少偶然违反的规范、尽管诚然、它的描述有点令人困惑。

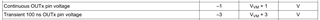

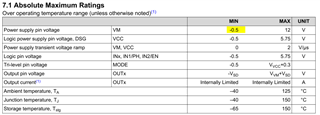

至于背景、我不确定。 我怀疑这是由于我们较新的芯片采用了更现代的制造工艺、导致它们更容易受到这种损坏。 我们所有最近的驱动程序都具有类似的规格-例如、下图来自 DRV8262:

请注意、如上述 pic 所示、该器件通常可承受略高的瞬态电压(小于100ns)、这在我们的所有器件中都很常见。

此致!

Jacob

太棒了! 负电压、但仍在规格范围内。

这在您自己的电路板上还是在我们的 EVM 上? 我建议订购 DRV8212EVM 并重复测试、只是为了确保不同的布局和元件不能轻松提高这种性能。

您的大容量电容是多少? 您是否可以尝试将其翻两倍或四倍、看看这是否会提高性能?

此致!

Jacob

嗨、Conor、

您推荐增大 CBulk 的原因在于需要抑制 VM 的瞬态过压/负电压、对吗?

是的、完全正确。

根据您的评论、我想知道上述波形中的 VM 是否会成为系统中的问题。

最小值-1V 可能会成为问题。 这超出了-0.5V 的器件规格。 您是否能够在输入上实施斜升/斜降加速、而不是立即将其打开/关闭? 这应该有助于降低这种影响。

尊敬的 Jacob:

您能否在输入上实施斜升/斜降加速、而不是即时打开/关闭输入? [报价]有必要确保 VM 额定值(负极侧)不会降至-0.5V 以下。

您曾提到"输入斜升/斜降加速"、但您具体如何构想实现这一点? 我问这个问题、因为这是我第一次听说斜升/斜降加速这一术语。谢谢!

Conor