工具与软件:

尊敬的专家:

DRV8860 DOUT 引脚是否可以悬空? 我们尝试使用2个芯片 DRV8860 (U1 DOUT 连接到 U2 DIN)、但不需要故障读取、因此 U2 DOUT 悬空。 有什么问题吗?

我们发现、当通电时、所有通道均已开启(内部 MOSS 已开启)、为什么会这样?

谢谢!

Joyce

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Joyce、您好!

澄清第二个问题:通电后无负载、所有 OUTx 均低至0V。 是因为我们在 OUTx 侧有一个灌电流吗?

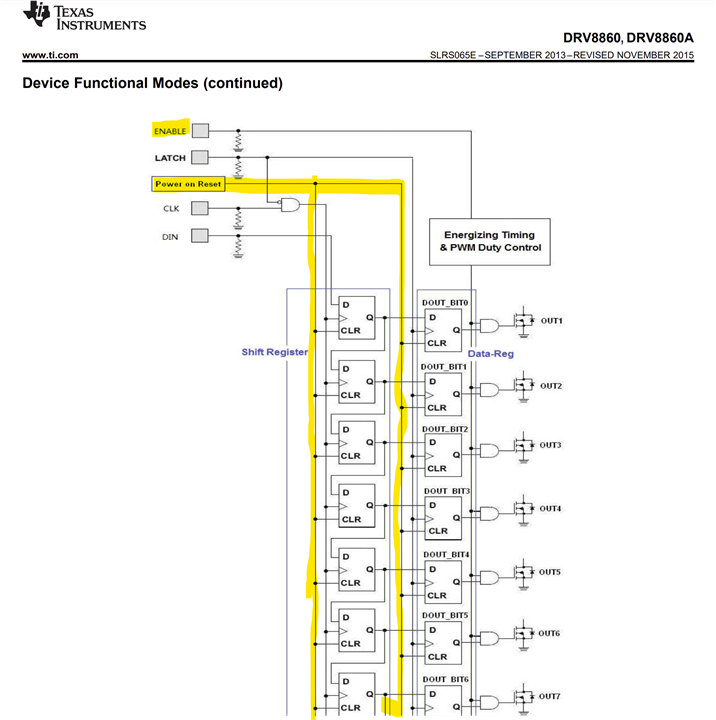

OUTx 是否有负载连接到 VM、没有向 CLK 施加时钟且没有锁存输入? 启用状态是什么? 在施加 VM 后的上电复位时、所有输出 D-FF 都被清除、这意味着 FET 不会导通。

以及第三个问题:尝试600kHz 时 CLK 无法控制输出。 如果我们将频率降低至100kHz、则可以实现此目的。 为了选择数据速率(CLK 频率)、我们应该参考哪种规格? 数字滤波器是否会影响这一点?[/QUOT]请参阅数据表中的最小 tCLK 规格-下屏幕截图。 因此、最大 CLK 频率为1/5us = 200kHz、具有对称的高电平和低电平时间。 因此低于200kHz 应该可以正常工作。 不支持600kHz。

此致、Murugavel

尊敬的 Murugavel:

是的、如果您不关心 Fault-Reg 内容或者不需要读取控制寄存器命令和读取数据寄存器命令、DOUT 可以保持悬空。

得到理解和解决。

OUTx 是否已将负载连接至 VM 并且未将时钟应用于 CLK 且无锁存器输入? 启用状态是什么? 在施加 VM 后的上电复位时、所有输出 D-FF 都被清除、这意味着 FET 不会导通。 [报价]未连接负载、无 CLK、无锁存器、使能保持高电平。 是因为这个30uA 的电流阱会在空载时将 OUTx 置于低电平?

[报价 userid="4637" url="~/support/motor-drivers-group/motor-drivers/f/motor-drivers-forum/1417753/drv8860-dout-pin-connection/5432048 #5432048"]请参阅数据表中的最小 tCLK 规格-下面的屏幕截图。 因此、最大 CLK 频率为1/5us = 200kHz、具有对称的高电平和低电平时间。 因此低于200kHz 应该可以正常工作。 不支持600kHz。 [报价]

为什么我在数据表中找不到此器件? 哦,我下载了中文版,它不是最新的! 没有屏幕截图中显示的部分! 我认为 TI.com 需要刷新中文版本。。。 理解并得到解决!

谢谢!

Joyce

Joyce、您好!

未连接负载、无 CLK、无锁存器、启用保持高电平。 是因为这个30uA 的灌电流在空载时会将 OUTx 置于低电平吗?

好的。 但是、您是否仅测量 OUTx 上相对于 GND 的电压、该电压为0V、因此确定 FET 正在导通? OUTx 是开漏输出、因此如果未连接负载、它将测量0V、无论泄漏电流是否为预期行为。

[报价 userid="531067" url="~/support/motor-drivers-group/motor-drivers/f/motor-drivers-forum/1417753/drv8860-dout-pin-connection/5432777 #5432777"]为什么我没有在数据表中找到此器件? 哦,我下载了中文版,它不是最新的! 没有屏幕截图中显示的部分! 我认为 TI.com 需要刷新中文版本。。。 理解并得到解决! [报价]如果中国数据表上有反馈链接、请使用它发送您的反馈。 谢谢。

此致、Murugavel