工具与软件:

您好!

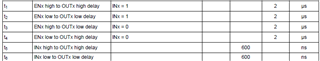

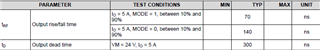

我有关于 DRV8962对有效 PWM 占空比估算的疑问。 数据表列出了这些参数、我认为这些参数应该是影响占空比精度的主要因素。

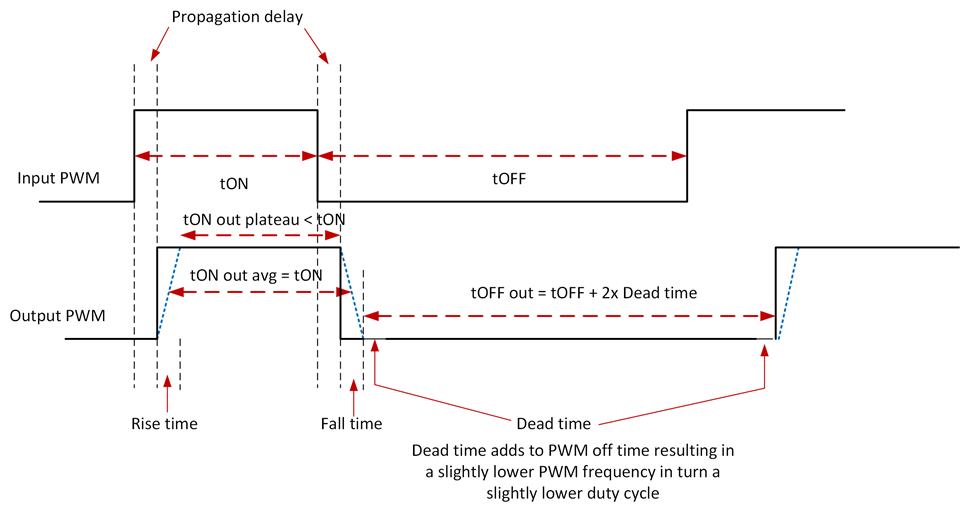

我们将 DRV8962 用作4个独立半桥驱动器、而不是 H 桥配置。 我假设有效的 Ton/Toff 将为 Ton/Toff 减去传播延迟产生的延迟时间+上升/下降时间+死区时间。 而有效占空比将为减去延迟时间后的 Ton/(Ton + Toff)。

混乱来自 T5/T6是否包括上升/下降时间和死区时间。 假设在切换之前很长时间启用了使能引脚、我没有考虑 T1/T2/T3/T4。

Teffective = Ton/Toff - T5/T6、因为 TRF 和 TD 包含在 T5/T6中

Teffective = Ton/Toff–(T5/T6 + TRF + TD)、因为 TRF 和 TD 不包括在 T5/T6中

如果上述理解有误、请告知我。 谢谢你。