主题中讨论的其他器件:、 DRV8328

工具与软件:

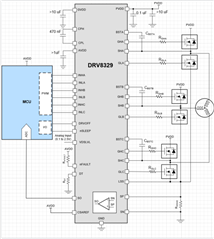

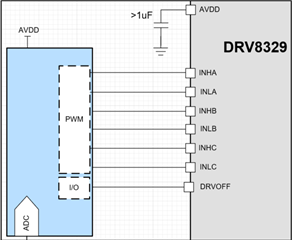

TI 的许多 BLDC 电机驱动器都具有称为 AVDD 的逻辑 LDO 输出。 添加该 LDO 的目的是为客户提供机会获得逻辑电平电压、以用于他们可能具有的板载其他元件。

该 LDO 的常见用途是为电机控制器 MCU 供电(假设 LDO 规格满足您的要求)。 但是、在系统中实现此功能时、需要了解上电序列的操作逻辑。

上电顺序:

- 为电机驱动器提供器件电源。 PVDD ->高电平

- 使器件退出睡眠模式。 nSLEEP ->高电平

- 等待器件经历数据表中指定的唤醒时间(tWAKE)

- 现在 AVDD LDO 已通电并可用于 MCU

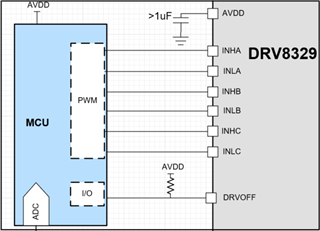

DRV8328/DRV8329/DRV8329-Q1数据表的典型应用部分(图1)发生了上电时序错误、即通过 AVDD 为 MCU 供电并具有相同的 MCU 控制 nSLEEP。 这会导致器件永远无法导通、因为 nSLEEP 不为高电平时、AVDD 的 MCU 电源永远不会接通。

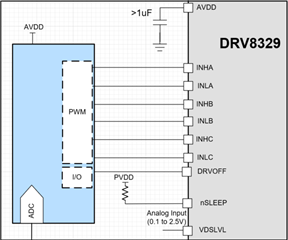

为避免此问题、我们建议通过电源电压 PVDD 为 nSLEEP 引脚供电。 正是由于这一考虑、我们使 nSLEEP 适用于处理更高电压的原因(请查看数据表以了解具体信息)。

有关通过 AVDD 为 MCU 供电(相对于 nSLEEP 和 DRVOFF)的潜在接线选项->用户首先选择 nSleep 和从 AVDD 为 MCU 供电的选项、然后为 DRVOFF 选择潜在的接线选项。

- nSLEEP

- 选项1–无睡眠模式

如果您的应用不需要睡眠模式、则可以将 nSLEEP 连接到 PVDD、以便在电源启动时直接打开器件。

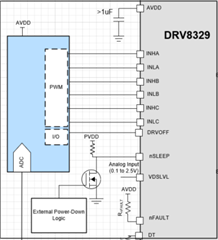

2.选项2–通过外部断电逻辑控制 nSLEEP

此选项可用于从睡眠模式获得低电流优势。 外部断电逻辑可用于使器件进入或退出睡眠模式。

- DRVOFF

- 选项1–MCU 上电后控制 DRVOFF 状态

在此选项中、MCU 需要从 AVDD 上电、然后可以使用 MCU GPIO 的 DRVOFF 启用/禁用驱动器功率级。

2.选项2–DRVOFF 具有连接至 AVDD 的上拉电阻

该选项让器件能够在驱动器上电后以安全状态启动、从而禁用驱动器输出。 当需要旋转电机时、用户可以使用 MCU 下拉电阻器关闭 DRVOFF。