Thread 中讨论的其他器件:UCC3626

工具与软件:

所有版本的数据表在一组表格中明确定义了操作模式。

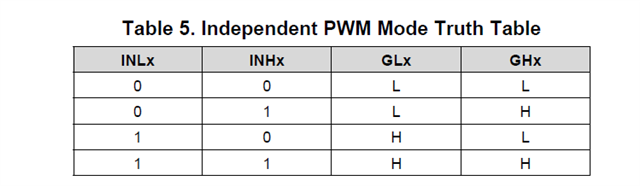

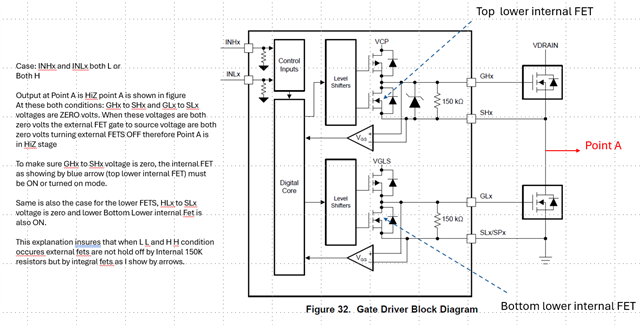

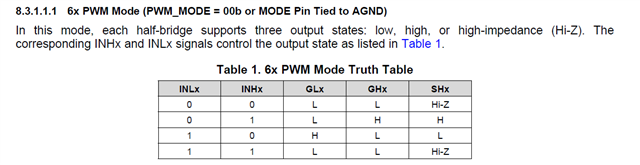

表1. 介绍了一种简单的栅极驱动器模式、其中 INHx 和 INLx 信号决定了栅极输出和电机绕组电压。 当 INHx 和 INLx 都为低电平(或两者都为高电平时)时、GLx 和 GHx 为低电平、SHx 为高阻态。

问题: 在这种情况下、这是否意味着高侧和低侧 MOSFET 的栅源电压都很低、以确保两个 MOSFET 都关断? 如果两者均关闭、这是否说明电机绕组连接(SHx)处于高阻抗(Hi-Z)状态?

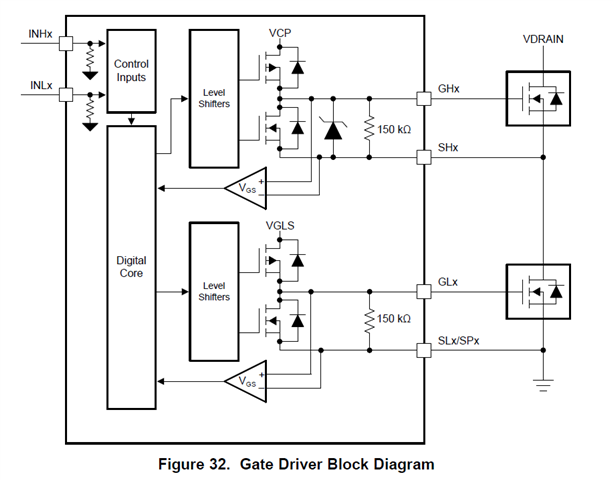

此外、当 SHx 处于 Hi-Z 状态时、它仍连接到8353的 SHx 引脚。 鉴于 GLx 和 GHx 均为低电平、而 SHx 处于 Hi-Z 模式、如何保证高侧和低侧 MOSFET 在这些条件下长时间保持关断?

还有第二个 Q:

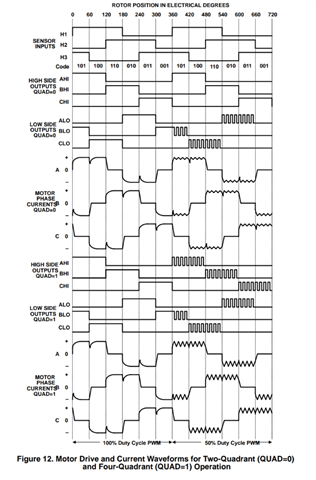

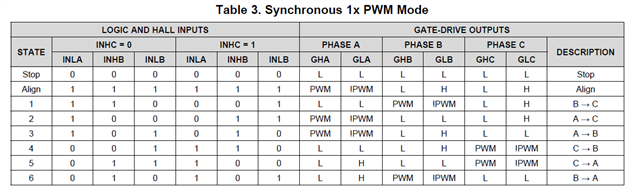

我看到、在同步模式下、根据霍尔条件、连接到三相桥高侧的电机绕组是使用顶部和底部 FET 的 PWM。 我假设这是上下下的转弯、但绝不会同时出现。 此模式的用途是什么? 电机电压可能是怎样的。 以及所使用的应用。

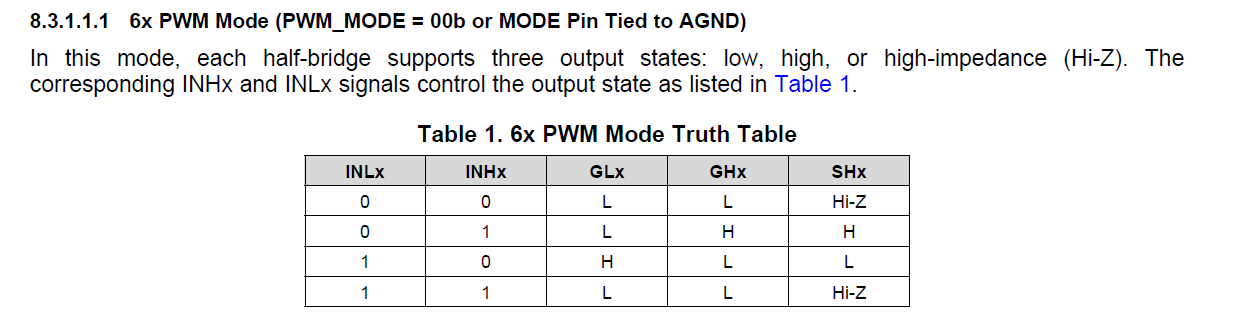

最后、如果我选择 Table 5。 与之前的表不同、SHx 信号的条件是什么?它未定义。 使用了什么模式表5? 如果我无限期地将 INHx INLx 保持在低电平或高电平、高电平和低电平 FET 是否会通过栅极至源极电压都关断? 8353的 SHX 引脚是什么?