Other Parts Discussed in Thread: DRV8873

工具与软件:

你好。

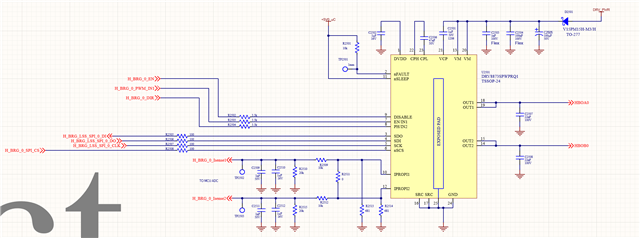

我们将使用 DRV8873 H 桥 IC。 我们发现、当器件关闭(未应用 VM)时会出现一个问题、该问题会导致 SPI 总线出现问题、从而阻止 MCU 读取总线上的其他器件并导致引导问题。

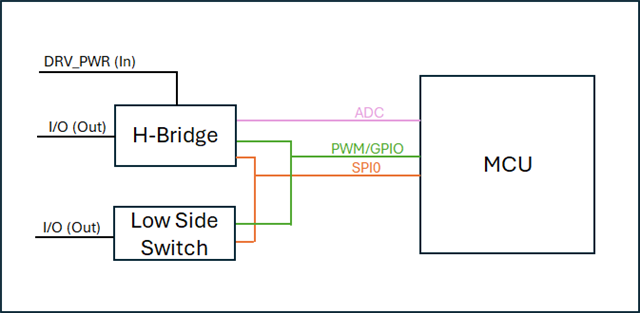

在该 pic 中、DRV_PWR 进行了开关、但并非始终开启。

更高级别的图

当施加 DRV_PWR (VM)时、总线可以恢复、我们可以与低侧开关通信。

我可以在数据表中的何处获得有关这方面的澄清

我们还没有在~ 1000个器件(每个器件3个板、每个器件4个 IC)上看到此问题、这一切似乎都发生在同一批次 C1V9上、这实际上是一个出厂问题、但所有支持尝试都将引导我来到这里。