工具与软件:

这是一个扩展了 DRV8329:启动时 nFault 情况的新主题

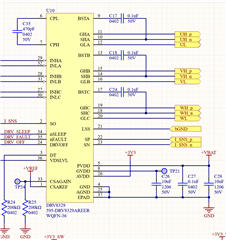

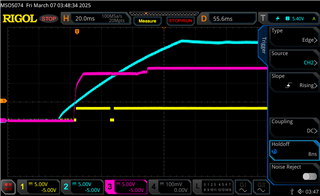

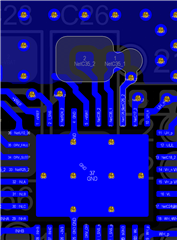

Based on your first waveform it seems that there is GVDD UV. Is the GVDD cap adequately sized and placed close to the driver GVDD pin?是的、我当时在查看故障表、并非常确定它是 GVDD UV、因为它没有出现。 GVDD 电容器为10µF、通过过孔连接到另一侧的布线非常短、电容器的一侧是我们要测量的位置、您可以看到电容器的 GND 连接位于芯片的接地焊盘正下方。 这里应该有很小的环路。

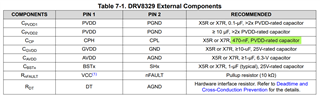

Can you test with 20V PVDD? GVDD is generated from CP below 18V and from an LDO above 18V.

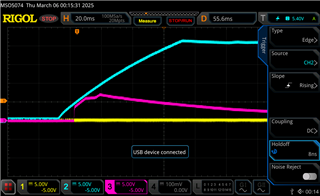

是的、我在使用电源、这里是 PVDD 变为21V 而 GVDD 在约10V 时停止的波形

Also note when DRVOFF being pulled high causes nfault to be pulled low, this is an expected behavior from the device. So I would remove this variable when testing.

是的、这可以很好地用于第二个分裂、我有一个硬件安全计时器、不断需要每1ms 切换一次以保持 DRVOFF 低电平、短高电平周期是因为此电路在附件+3V3_SW 打开之前不运行、在此之前、DRVOFF 处于该中点、只有在生成 DRVOFF 关闭 GVDD 时才应该是问题 如果我正确阅读数据表、情况并非如此。

Also what is nsleep doing during this time?

nSleep 此刻连接到 PVDD、我的是由 MCU 引脚控制、但是由于 MCU 由该芯片的 AVDD 供电、因此您的循环逻辑需要 AVDD 来使 nSleep 为高电平、但您需要高电平 nSleep 以使 AVDD 无法正常工作、因此我进行了修改。 是否要求该电阻为上拉电阻、而不是直接连接到 PVDD?

下面是供参考的相关原理图: