Other Parts Discussed in Thread: MSPM0L2228, LP-MSPM0L2228, MSP430FR6007, MSP430FR6047

器件型号: LP-MSPM0L2228

Thread 中讨论的其他器件: MSP430FR6007、MSPM0L2228、 MSP430FR6047

工具/软件:

您好、

我尝试 使用两个板上的 UART1 在两个 LP-MSPM0L2228 板之间发送数据。

我们的最后一个用例是我们大部分时间都需要在低功耗模式下运行的设置、这意味着我们不能使用 HFCLK — 因此选择了 LFCLK (LFXT 32.768kHz)。

UART 必须以 9600 波特和 8 个数据位、无奇偶校验位和 2 个停止位进行通信、才能使用我们的现有设置。我们的现有设置包含 MSP430FR6007 器件以及非 TI 器件、所有器件都从 32.768kHz 晶体运行其 UART。

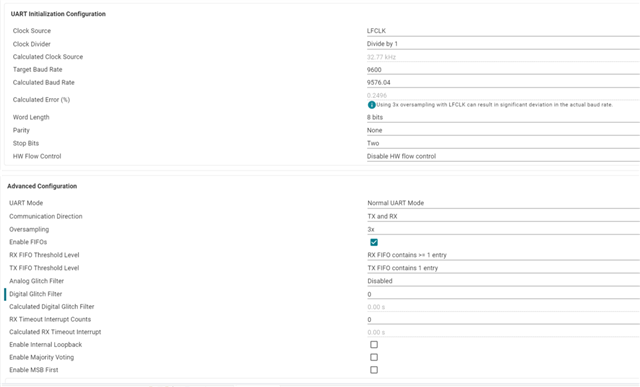

测试时、我使用“uart_echo_interrupts_standby"示“示例、然后在引脚 PA8 + PA9 上切换到 LFXT 和 UART1。 此外、我还为 LFCLK 启用了引脚 PA27 上的 CLKOUT。

对于 RX 工程、我还在 PA25 上有一个调试引脚、指示示例代码何时检测到接收的数据不一致。

如果我为 UART 设置以下设置、则可以实现无错误通信:

源:MSPM0L2228 8N2(9576.04 波特)->目标:MSPM0L2228 8N1(9709.04 波特) ->确定

来源:MSPM0L2228 8 1 波特率为 9576.04 ->目标:MSPM0L2228 8N1、波特率为 9709.04 ->正常

如果我为两个 UART 设置以下对称设置、我会执行该操作 不会 获取无差错通信:

源:MSPM0L2228 8N2(9576.04 波特)->目标:MSPM0L2228 8N2(9576.04 波特) ->失败

源:MSPM0L2228 8E1(9576.04 波特)->目标:MSPM0L2228 8E1(9576.04 波特) ->失败

1) 设置 2 个 MSPM0L2228 评估模块时。 一个用于 TX、一个用于具有相同设置(波特率,奇偶校验和停止位)的 RX,那么我没有获得无差错通信 — 怎么回事? 我设置的项目是错误的、还是这种行为符合预期?

我还很难获得我们的非 TI 处理器来 从 MSPM0L2228 接收无差错传输。 不过、我们以前的非 TI 处理器可以顺利通过 MSP430FR6007 实现。

2) 是否有更多参数可以在 MSPM0L2228 上调整/调整、以便使非 TI 处理器正确接收来自 MSPM0L2228 的传输。 到目前为止、我是否已调整奇偶校验位和停止位以及波特率 (IBRD + FBRD)?

3) 据我所知、MSP430FR6007 有一个寄存器、我们可以在该寄存器中修改位调制模式。 MSPM0L2228 的整数和分数部分具体如何工作、这可以解释我们为什么看到通信失败?

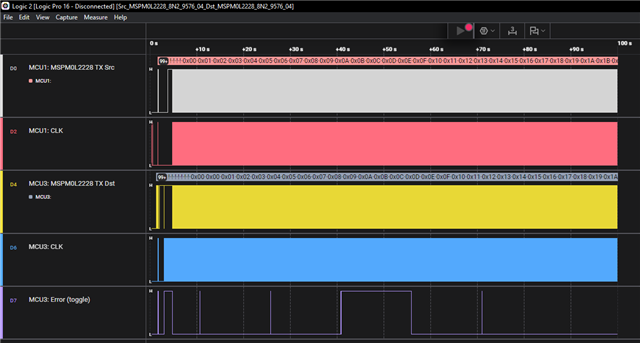

下面、我提供了 3 张图片、展示了当两个 MSPM0L228 模块相互通信时捕获的逻辑分析仪的情况。

两个电路板均设置为 8 个数据位、无奇偶校验位和 2 个停止位、波特率为 9576(通过 syscfg)。

发送代码发送一个字节 — 使其递增,然后再次发送。

接收代码会接收一个字节并验证其是否比前一个接收到的字节高 1 — 如果不切换,则切换 PA25 — 无论该字节是否匹配,都会传输该字节。

MCU1:来自源端 MSPM0L2228 板的 MSPM0L2228 TX src // TX //(PA8_UART1-TX(源端 MSPM02228 板))

MCU1:来自源板的 CLK// LFCLK //(PA27(源 MSPM02228 板))

MCU3: 来自目标 MSPM0L2228 板的 MSPM0L2228 TX DST// TX(该板回显从源板接收到的内容) //(PA9_UART1-RX(目标 MSPM02228 板))

MCU3:CLK //来自目标板的 LFCLK //(PA27(目标 MSPM02228 板))

MCU3:错误(切换) //来自目标板的 GPIO、每次该板接收到一个顺序错误的字节时、都会切换该 GPIO。 通常会一个接一个地出现两个切换–错误字节// (PA25(目标 MSPM02228 板)) 的每侧各一个

PA8_UART1-TX(源 MSPM02228 板)连接到 PA9_UART1-RX(目标 MSPM02228 板)

两块电路板之间连接的接地端。

第一张图片展示了两个电路板之间的整个通信(几百)。 MCU 中的每个状态移位:错误(切换)指示按顺序接收到的字节。

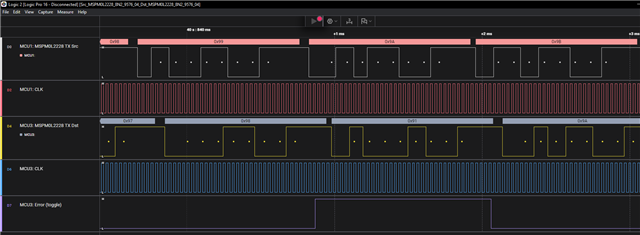

第二张图片显示了其中一个错误的特写。 错误地将字节 0x99 接收为 0x91。

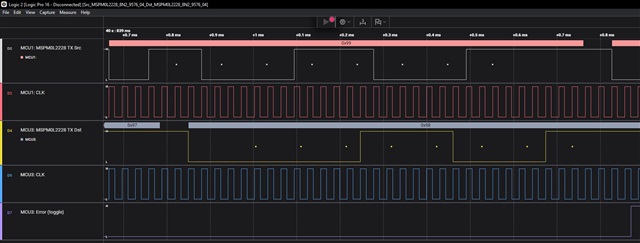

最后一张图片进一步放大、因此更容易看到两个电路板的时钟。

如果需要更多信息、请告诉我。

此致

BUE