我对MSP430FT6989的勘误表数据表中讨论的其中一个问题有疑问:

当设备处于SPI模式时,USCI41 eUSSCI模块功能UCBUSY eUSIA模块位卡在1位。 说明在SPI模式下配置eUSCIA时,最后的传输位从0更改为1,UCBUSY位被卡在1。 这发生在时钟相位和时钟极性选项(UCAxCTLW0.UCCKPH和UCAxCTLW0.UCCKPL位)的所有四种组合中。 没有数据丢失或损坏。 由于USSCBUSY位被卡在1,时钟请求保持启用状态,并在低功耗模式操作中增加了额外的电流消耗。 解决方法检查传输或接收中断标志UCTXIFG/UCRXIFG而不是UCBUSY,以了解UCAxTXBUF缓冲区是空的还是可以容纳下一个完整字符。

我已经确定这是一个问题-或者已经验证过-但是如果我使用UCA0作为SPI从属设备;我想在接收时传输SPI数据包;我不太清楚确定端口是否仍然繁忙的最佳方法; 特别是在检查SPI数据包是否已传输时。

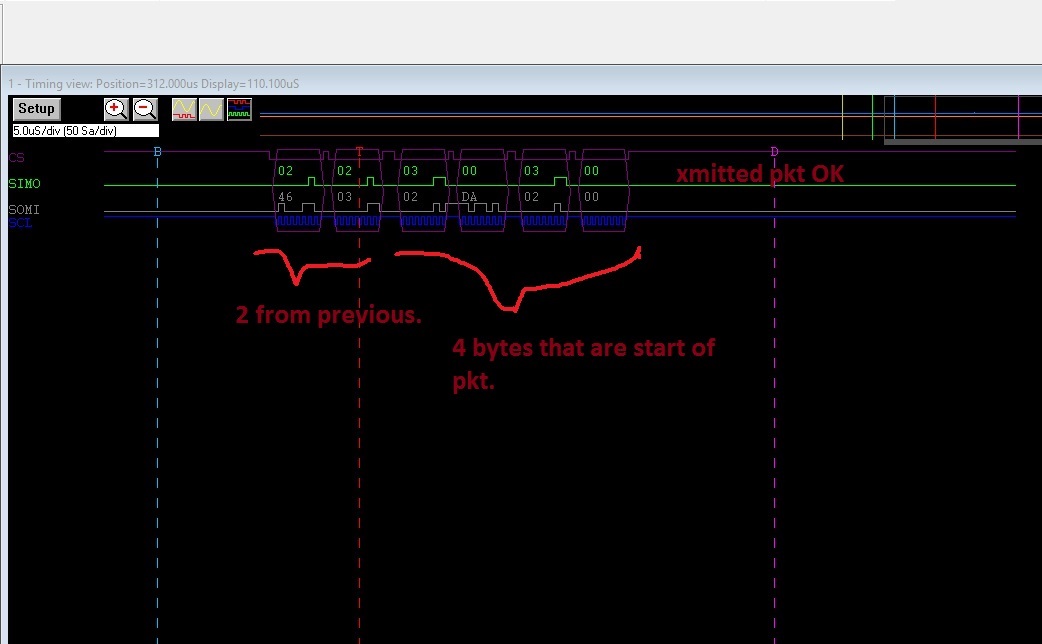

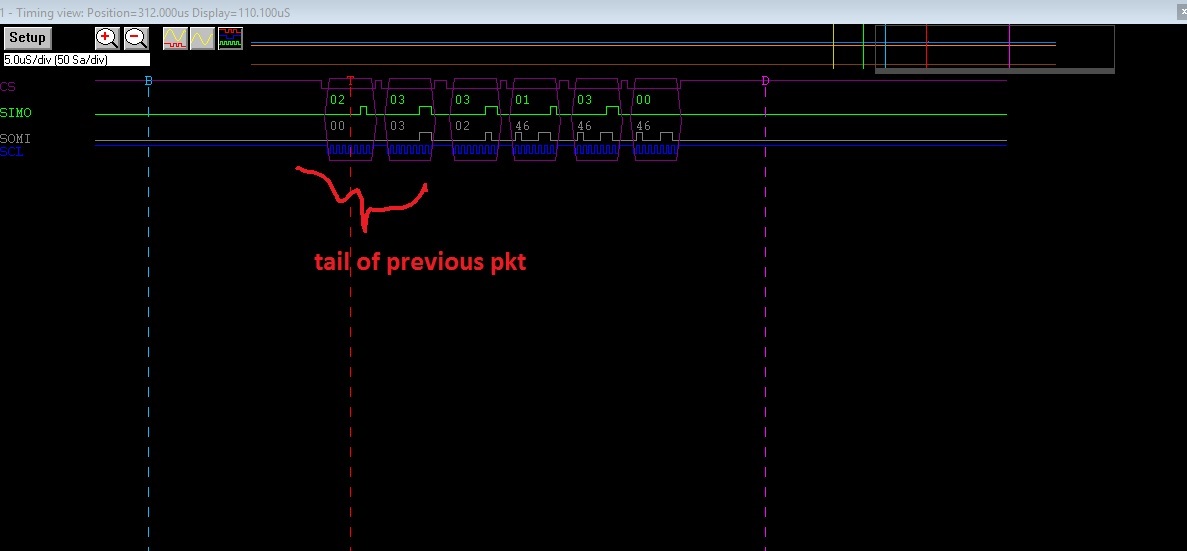

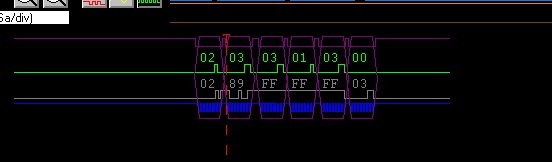

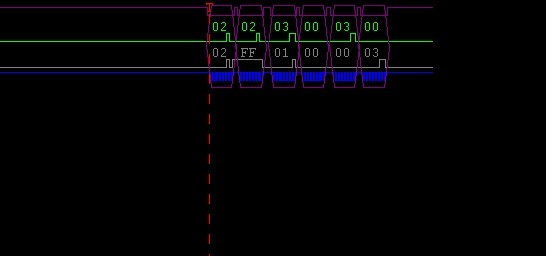

现在,我看到发送的数据包与我可以通过2个字节分辨的数据包不一致,这意味着前两个字节来自上一个数据包。

我想USCI45在SPI从属模式下不是问题,对吗?

USCI45 eUSCI模块功能意外SPI时钟可能拉伸说明在极少数情况下,在SPI通信期间,第一个数据位的时钟高相位可能会明显拉伸。 SPI操作按预期完成,不会丢失数据。 仅当USCI SPI模块时钟(UCxCLK)与系统时钟(MCLK)不同步时,才会出现此问题。 解决方法确保USCI SPI模块时钟(UCxCLK)和CPU时钟(MCLK)相互同步。

这是相当简单的;但我想知道确定变速器何时仍在进行的最佳方法,因为这是从变速器-由于勘误表,这样的方法不起作用:

而( EUSCI_A_SPI_isBusy(EUSI_A0_base)== EUSCI_A_SPI_BUSY )//SPI仍在发送数据? -勘误表

;

我也在使用DMA - 2个通道- 1个用于接收,1个用于传输。

有关此勘误表:

DMA7 DMA模块功能DMA请求可能导致中断丢失说明如果DMA请求在使用读-修改-写指令访问包含中断标志的模块寄存器期间开始执行,则来自同一模块的新到达中断可能会丢失。 在DMA执行之前设置的中断标志不会受到影响,而是保持设置状态。 解决方法1. 使用对中断向量寄存器的读取来清除中断标志,而不使用readmodife-write指令。 或2. 激活这些中断时,在包含中断标志的特定模块寄存器的读-修改-写指令期间禁用所有DMA通道。

是否可以执行此操作:

dma_disableTransferDuringReadModifyWrite();

DMACTL0 |= DMARMWDIS; //和/或?

DMACTL1 |= DMARMWDIS; //和/或?

谢谢!

John W.