主题中讨论的其它部件: SN74AUP1G34

我在将近一年前发布了关于此问题的文章:

https://e2e.ti.com/support/microcontrollers/msp430/f/166/t/58.5032万

但我想重新回顾一下,看看我的解决方案是否可行。

简而言之,我想将CP2102 USB-转 串行适配器嵌入MSP430G2553电路中,以便只需使用USB电缆和正确的软件即可执行固件更新。 我不会使用测试和/重置时的特殊信号模式进入BSL,而是需要使用DTR从PC软件重置处理器。 问题是CP2102在断电时会在其所有I/O引脚处吸入电流,除非 通过连接的USB电缆通电,否则始终会断电。 因此,如果我将DTR连接到 处理器的/Reset引脚,该引脚将被夹紧在较低的位置,这是不好的。 我之前问过串联使用电容器的问题,但担心当DTR恢复高电平时会发生什么情况-理论上,/Reset引脚处会出现6.6V的峰值。

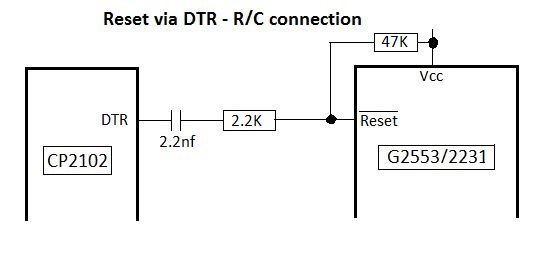

我最后完成了这个电路:

该电容器是标准2.2nF值,应该仍允许SBW JTAG闪存,但它连接到DTR,当CP2102断电时,DTR在接地时有效。 当DTR变高时,2.2 K电阻器用于将保护二极管电流限制在数据表中指定的2 mA以下。

这似乎工作正常。 当DTR变低时,负向复位脉冲几乎接地, 并在大约100 usec的时间内保持在2V以下。

我只是想确保我没有忽视任何事情。 如果有人发现问题,请发布。

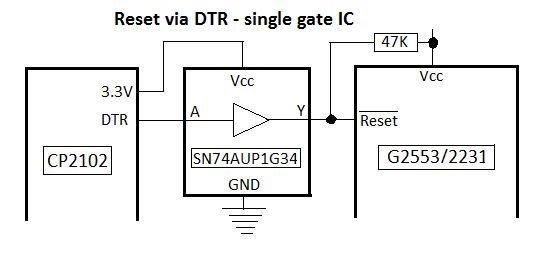

顺便说一下,使用单栅无反相缓冲器的原始线程中建议的解决方案也会起作用。 SN74AUP1G34似乎是实现这一目的的最佳选择。