请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:MSP430F5419A 各位专家、您好!

我对 I2C SCL THIGH 和 TLOW 有一个问题。

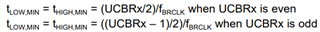

DS 中提供了计算股部和股部最小值的公式。

我客户的 I2C 具有以下设置。

- UCBRx:64

- fBRCLK:25、000、000 (25MHz)

- I2C 主设备

对于此设置、大腿和小腿为:

低电平、最小值=股部、最小值=(UCBRx/2)/fBRCLK

= 64 / 2 / 25000000

= 1.28us

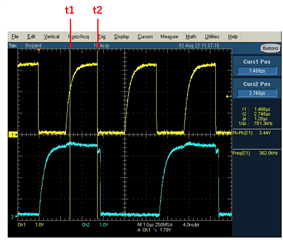

客户的 I2C 波形如下所示。

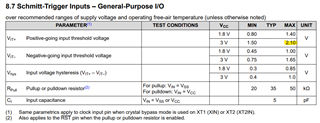

Δ I 为1.28usec。T1为 SCL 为2.1V (正向输入阈值电压)ΔT。

由于客户的波形响应缓慢、它相当于 tHIGHMIN 的值、因此无法判断它是否符合 tHIGHMIN 的要求规格。

请告诉我们:

•需要更快的波形响应?

•此波形是否有问题?

此致、

Sasaki