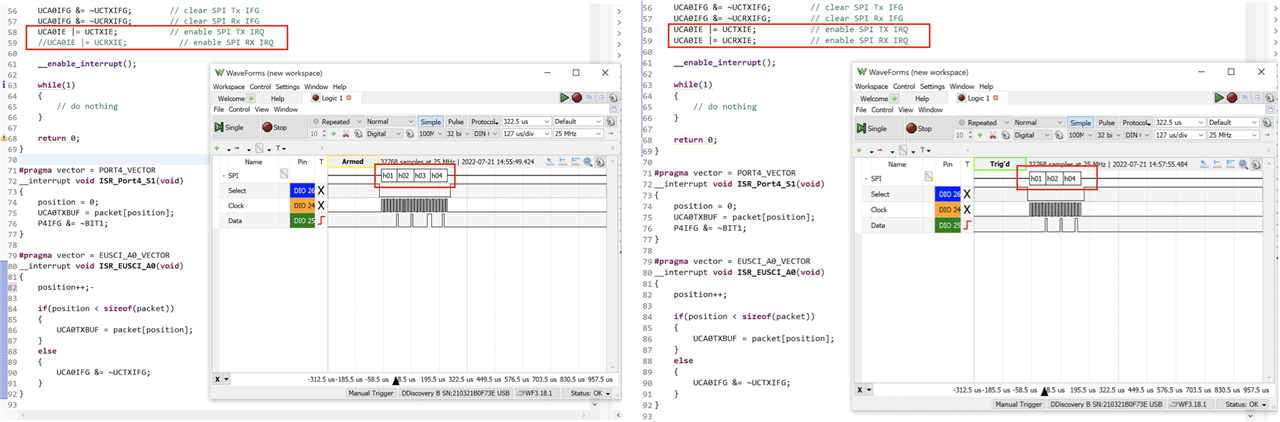

我的代码非常简单-通过 SPI 发送包含四个十六进制{0x01、0x02、0x03、0x04}的信息包。 一切都正常、直到我在 进入 主循环之前添加一个额外的代码行、启用 UCRXIE 中断。

在启用 UCRXIE 之前、数据线发送{0x01、0x02、0x03、0x04}。 启用 UCRXIE 后、数据线始终 发送 {0x01、0x02、0x04}-一个十六进制短整型值、出于任何原因、始终缺少0x03。 在 我能够解决这个丢包问题之前,我不能实现 RX 的中断功能-- 最后、我将使用一 个 EUSCI_A0_Vector 来处理 UCTXIE 和 UCRXIE 中断、方法是检查哪些标志 UCTXIFG 和 UCRXIFG 已设置、我接收的 RX 数据包 取决于我在 SPI 线路上发送的 TX 数据包。

我在这里附上了屏幕截图和代码。

#include <msp430.h>

char packet[] =

{

0x01, 0x02, 0x03, 0x04 // packets

};

unsigned int position;

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // stop watchdog timer

UCA0CTLW0 |= UCSWRST; // put eUSCI_A0 into SW reset

UCA0CTLW0 |= UCSSEL__SMCLK; // choose 1MHz SMCLK as BRCLK

UCA0BRW = 10; // 1MHz divide by 10 = 100kHz

UCA0CTLW0 |= UCSYNC; // set bit to SPI mode

UCA0CTLW0 |= UCMST; // set bit to SPI master mode

UCA0CTLW0 |= UCMSB_1; // UCMSB_0=LSB; UCMSB_1=MSB

UCA0CTLW0 |= UCMODE1; // 4-wire STE LOW (10b)

UCA0CTLW0 &= ~UCMODE0; // ..

UCA0CTLW0 |= UCSTEM; // enable STE output pin

P1SEL1 &= ~BIT5; // P1.5 (UCA0SCLK)

P1SEL0 |= BIT5; // P1.5 ..

P1SEL1 &= ~BIT7; // P1.7 (UCA0SIMO)

P1SEL0 |= BIT7; // P1.7 ..

P1SEL1 &= ~BIT6; // P1.6 (UCA0SOMI)

P1SEL0 |= BIT6; // P1.6 ..

P1SEL1 &= ~BIT4; // P1.4 (STE)

P1SEL0 |= BIT4; // P1.4 ..

P4DIR &= ~BIT1; // P4.1 (SW1) clear as input

P4REN |= BIT1; // P4.1 (SW1) enable pull-up/down resistance

P4OUT |= BIT1; // P4.1 (SW1) pull-up

P4IES |= BIT1; // P4.1 (SW) interrupt edge select: high-to-low transition

PM5CTL0 &= ~LOCKLPM5; // get out of LPM

UCA0CTLW0 &= ~UCSWRST; // get out of SW reset

P4IFG &= ~BIT1; // P4.1 (SW1) clear IFG

P4IE |= BIT1; // P4.1 (SW1) enable IRQ

UCA0IFG &= ~UCTXIFG; // clear SPI Tx IFG

UCA0IFG &= ~UCRXIFG; // clear SPI Rx IFG

UCA0IE |= UCTXIE; // enable SPI TX IRQ

UCA0IE |= UCRXIE; // enable SPI RX IRQ

__enable_interrupt();

while(1)

{

// do nothing

}

return 0;

}

#pragma vector = PORT4_VECTOR

__interrupt void ISR_Port4_S1(void)

{

position = 0;

UCA0TXBUF = packet[position];

P4IFG &= ~BIT1;

}

#pragma vector = EUSCI_A0_VECTOR

__interrupt void ISR_EUSCI_A0(void)

{

position++;

if(position < sizeof(packet))

{

UCA0TXBUF = packet[position];

}

else

{

UCA0IFG &= ~UCTXIFG;

}

}