尊敬的论坛:

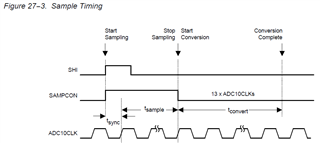

我对 MSP430F1xx 手册中的图18-3有点困惑、其中显示了 ADC10如何获取样本。

请注意、如果需要 对更高频率的交流信号进行数字化、精确采样就变得很重要。

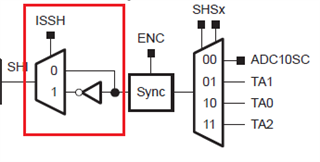

假设 Tmer_A (TA)模块输出信号执行采样(SHi=OUT1上升沿)(定期)。

假设两个 TA 模块 ADC10CLK 也来自 SMCLK。 TA 对时钟的上升沿进行计数。

TA OUT (和 SHI)在 SMCLK 的上升沿改变其状态。

在此设置中、SHI 触发上升沿与 ADC10CLK 完全同相 、因此根据图18-3、'tSYNC'->0。 它是否 会在 采样时间间隔内引起抖动(内部触发器没有确保建立/保持时间),例如在4*Tclk / 5*Tclk 之间随机切换?

还是某些内部机制 allways 提供 ADC10控制寄存器中定义的采样间隔(通过 SHTx 位)?

谢谢 、此致、

Joseph