主题中讨论的其他器件:MSP430WARE

我使用 driverlib SDKTimer_A_outputPWM() 函数在 TA0.1上生成 PWM 信号。 PWM 信号以正确的占空比产生、但周期是我预期的两倍。

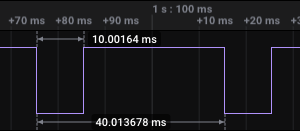

根据我的计算、周期应为20ms、但生成的波形的周期为40ms。 SMCLK 以大约2MHz 的频率运行。 我已使用验证了这一点CS_getSMCLK()。 我要将时钟信号除以40、再除以50 KHz。 1000 / 50 KHz 应该是20毫秒、还是我缺少什么?

GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_P1, GPIO_PIN1, GPIO_SECONDARY_MODULE_FUNCTION); Timer_A_outputPWMParam TimerParams; TimerParams.clockSource = TIMER_A_CLOCKSOURCE_SMCLK; TimerParams.clockSourceDivider = TIMER_A_CLOCKSOURCE_DIVIDER_40; TimerParams.timerPeriod = 1000 - 1; TimerParams.compareRegister = TIMER_A_CAPTURECOMPARE_REGISTER_1; TimerParams.compareOutputMode = TIMER_A_OUTPUTMODE_RESET_SET; TimerParams.dutyCycle = 750; Timer_A_outputPWM(TA0_BASE, &TimerParams);