数据表似乎建议定时器模块的外部信号输入可以与系统频率一样高。

如果器件以25MHz 运行、定时器是否能够支持高达25MHz 的输入信号、并且仍然在每个上升沿递增计数器? 这假设占空比为50%。

CC26x0等器件建议需要一个或两个系统时钟周期来锁定上升沿并更新计数寄存器...

检测到边沿后、该器件是否在第一个系统时钟的上升沿更新计数寄存器?

如果是、在检测到下一个上升沿并将其锁定到计数寄存器之前、信号下降沿需要多长时间?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

数据表似乎建议定时器模块的外部信号输入可以与系统频率一样高。

如果器件以25MHz 运行、定时器是否能够支持高达25MHz 的输入信号、并且仍然在每个上升沿递增计数器? 这假设占空比为50%。

CC26x0等器件建议需要一个或两个系统时钟周期来锁定上升沿并更新计数寄存器...

检测到边沿后、该器件是否在第一个系统时钟的上升沿更新计数寄存器?

如果是、在检测到下一个上升沿并将其锁定到计数寄存器之前、信号下降沿需要多长时间?

Darren、您好!

我想您不是说输入计时器时钟、而是实际尝试在捕获模式下将25MHz PWM 输入测量到计时器中? 您希望它能确切地工作吗? 是否检测到几个1计数的脉冲?

计时器中的所有内容都应由计时器时钟驱动、而不是系统时钟、尽管它们可能具有相同的速度或时钟源。

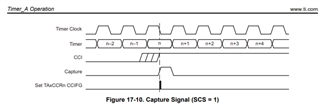

根据用户指南的图12-10、捕捉在定时器时钟的下降沿被识别。

对于您的最后一个问题、数据表显示 Timer_A 和 Timer_B 在定时器捕捉上可以检测到的绝对最快脉冲为20ns、因此它应该能够检测到一个25MHz 脉冲。

即使这样、实际处理中断并读取计时器寄存器所需的时间也要比脉冲更长、因此我不确定这里的用例是什么。

谢谢、

JD

JD、您好!

编辑: 我不理解如何使用捕获模式...您必须在捕获事件后读取定时器值、否则"...如果在读取第一次捕获的值之前执行了第二次捕获...COV 已设置"

我不是说捕获单个脉冲。 我打算使用计时器输入进行事件捕获。 基本上、您将 TCA0CLK 输入设置为一个外部引脚、然后对这个引脚施加一个信号。

来自 TRM:

16位定时器/计数器寄存器、TAxR、随着时钟信号的每个上升沿递增或递减(取决于运行模式)。

我将讨论使用外部信号作为"时钟信号"、以便每当该外部信号出现上升沿时 TAxR 就会递增/递减。

我的理解是这是可行的、但在25MHz 时不可行。 主要原因是系统时钟以25MHz 的频率运行、但要锁定检测到的边沿并更新 TAxR 寄存器、需要2个系统时钟(25MHz)周期。

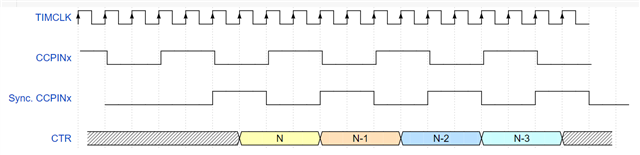

我做了一个示例、并附加了图像。 在这里、TIMCLK 将是系统时钟(25MHz)

然后、CCPINx 将是 TA0CLK 引脚的实际信号输入。

然后、在 CCPINx 变为高电平后的两个 TIMCLK 上升沿之后、这会被锁定、在 TIMCLK 的下一个上升沿上、TAxR 会被更新。 这有效地将25MHz 限制为25MHz/4 = 6.25MHz、对吧?

您好 Darren、

我仍然不能完全掌握你要做的事情,但我开始跟随。

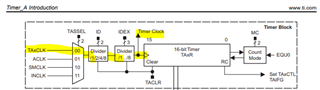

首先、似乎是使用外部信号作为计时器时钟源。 这将通过 MCU 上的 TAxCLK 引脚来完成。 正如 Bruce 提到的、数据表指出外部 TAxCLK 的频率最高可达25MHz。

这个时钟可以在没有分频器的情况下馈入、并且将成为计时器时钟。

TAR 将在定时器时钟的每个上升沿递增/递减。

听起来我们到目前为止同意这一点、我希望输入信号能够在高达25MHz 的频率下工作。 我不明白您的担忧超出了这一点。

您在哪里看到系统时钟门控 TAR 递增?

谢谢、

JD

JD、您好!

我弄清楚了我遇到的问题。

1) 1)最初假设任何 MCU 可以接受计时器的外部输入、则会使用此信号更新计数器

2) 2)然后我了解到、对于 CC26x0器件、它们"无法"执行此操作-它们使用"主"时钟来"计时"边沿

对于 SBD、请参阅 https://www.ti.com/lit/ug/swcu117i/swcu117i.pdf 的 p1190 -有一个"PERDMACLK"进入"边沿检测"块

然后、p1193上有注释

这让我感到困惑。

现在我知道、器件可能会说它具有计时器时钟的外部输入、但这并不一定意味着计数值会直接在该外部时钟上更新。

一些器件直接使用外部时钟来更新计时器计数(MSP430F5528)、而其他器件使用主时钟来同步(抗噪?) 边沿并将检测移入计时器计数器(CC26x0)

我明白了。

谢谢!

Darren