Other Parts Discussed in Thread: MSP430F67641A, MSP430F6736

主题中讨论的其他器件: MSP430WARE、 MSP430F6736、 MSP-TS430PZ100B

尊敬的团队:

我们正在根据您的评估模块设计多相能量计及其纯粹的定制设计。 电路的核心部分保持不变(电压、电流测量、引脚映射)、但仅更改了输出(显示屏、外部通信)。

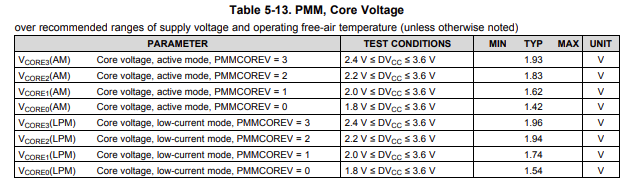

我可以使我们的原型正常工作、但我看到内核电压有一些问题。 根据您的示例代码、我使用下面的将内核电压设置为3V、但仍然可以看到导通电压(引脚23 VCORE)始终为1.8V、将晶体限制为8MHz。 (控制器由3.3V 电源供电)

这是我从您的样片中选择的以下代码。 如果我没有什么东西,可以请你给我一个好机会吗? 或者、内核电压取决于我们目前不关注的一些辅助电源。

注意:目前我们不使用任何辅助电源、外部32kHz 晶体未安装并保持开路。

- AuxVCC1&2被接地

-DVSYS (20&74)已接地并盖住接地

- AuxVCC3保持开路、未安装外部32kHz 晶体

空 System_Init()

{

PMMCTL0_H = PMMPW_H;

SVSMHCTL&=~SVSMHRRL_7;

SVSMHCTL|=SVSMHRRL_4;

AUX3CHCTL = AUXCHKEY | AUXCHEN | AUXCHC_1 | AUXCHV_1;

AUXCTL0 = AUXKEY;

AUXADCCTL = AUXADC | AUXADCSEL_0 | AUXADCR_0;

AUXCTL2 |=AUX0LVL_6 +AUX1LVL_5 + AUX2LVL_5;

AUXIE |=(AUX0SWIE | AUX1SWIE | AUX2SWIE | AUX0DRPIE | AUX1DRPIE | AUX2DRPIE | AUXMONIE);

PMMCTL0_H = 0;

SetVCore (3);

_bis_SR_register (SCG0);//禁用 FLL 控制循环*

UCSCTL6 =(UCSCTL6 | XT1DRIVE_3);//针对 XT1启动的最高驱动设置

while (SFRIFG1和 OFIFG)

{

/*检查 OFIFG 故障标志*/

UCSCTL7 &=~(DCOFFG | XT1LFOFFG | XT2OFFG);/*清除 OSC 故障标志*

SFRIFG1 &=~OFIFG;/*清除 OFIFG 故障标志*/

}

UCSCTL6 =(UCSCTL6 &~(XT1DRIVE_3));//将驱动降低至较弱的状态*/

UCSCTL0 = 0;

UCSCTL1 = DCORSEL_6;//将 RSELx 设置为 DCO = 25MHz */

UCSCTL2 = FLLD__4;

UCSCTL2 |=(192 - 1);//将 DCO 乘法器设置为25MHz */

/*将 FLL 设置为32768*4*192 => 25165824Hz */

_BIC_SR_register (SCG0);/*启用 FLL 控制环路*

UCSCTL5 |= DIVS__1 | DIVA_32;

UCSCTL4 = SELM__DCOCLK | SELESS__DCOCLK | SELA_XT1CLK;/* 24MHz MCLK、24MHz SMCLK、ACLK (25MHz/32)*/

_DELAY_CYCLES (100);

}

问题2:您是否有完整的能量计工作示例代码(https://www.ti.com/tool/EVM430-F67641)?

我可以访问其原理图、但无法直接获取完整的工作项目。 我得到了一些代码、它太难将其组合在一起以获得一个可编译的代码。

提前感谢、

Surya