主题中讨论的其他器件:MSP-EXP430F5529LP、

您好!

您能就以下干扰提供建议吗?

问题1. 这是部件的已知现象吗?

问题2. 您是否认为这种干扰在任何情况下都是有害的,会导致通信错误? 我的客户担心干扰形式或时间变化。

我的客户使用其中一个 USCI 作为380kHz 的 I2C 主设备。

当 SCL 下降为一个启动条件时、它们在 SDA 上发现一个毛刺脉冲。

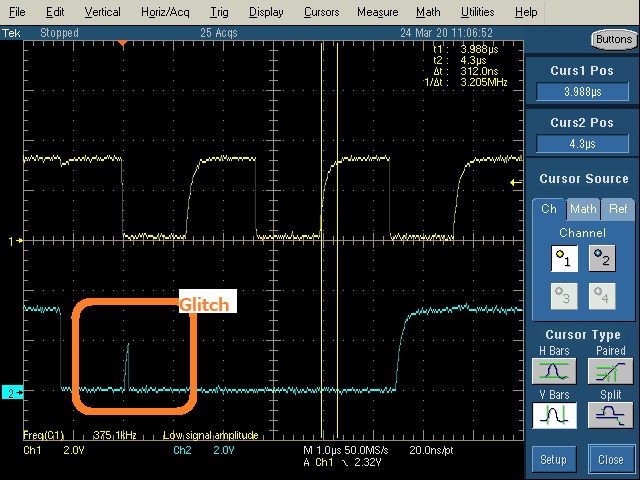

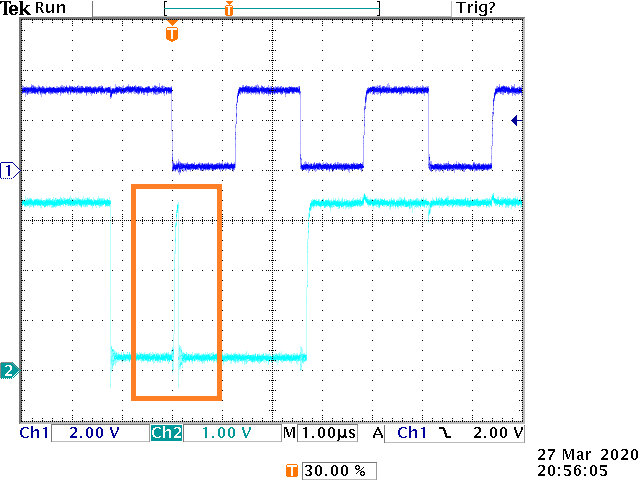

下面提供了一个示波器屏幕。 CH1 (上部)= SCL、Ch2 (下部)= SDA。

请在 SCL 的第一个下降边沿之后的 Ch2 = SDA 上找出毛刺脉冲。

我发现一个线程与这种现象非常接近:

https://e2e.ti.com/support/microcontrollers/msp430/f/166/t/237128