问题:

- MSP430FR2676是否具有增强型时钟系统?

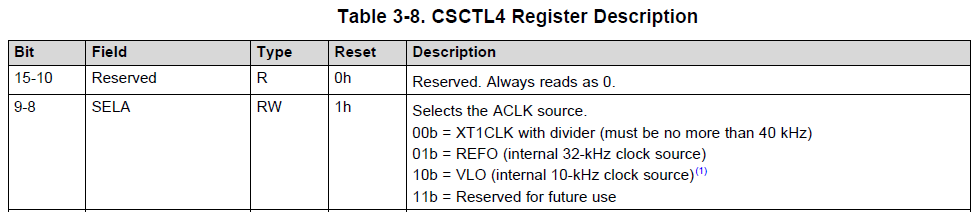

- 我可以让 VLO 作为 ACLK 的源吗?

非常感谢:)

威利

------------------------------------------

很难从数据表或用户指南中得知:(我猜是-增强型 CS)

- 数据表第55页(SLASE05C)-状态:

"辅助时钟(ACLK):该时钟来自外部 XT1时钟、内部 VLO 或内部

REFO 时钟高达40kHz"。因此、我们可能会认为这是一个较新的器件、并且具有增强型时钟系统-但只能达到16MHz 而非24MHz (增强型 CS)-因此再次令人困惑。

- 用户指南(SLAU445I)第98页-表3-1未列出 MSP430FR2676:

- 因此、不确定是否增强

- 我在搜索时知道有一个与此相关的帖子-但对于不同的器件型号。大约1年前-所以如果可以的话、我会再次询问。