Other Parts Discussed in Thread: MSP430F148

主题中讨论的其他器件:MSP430F148

团队、

我们正在使用 I2021进行原型设计、并有一些问题、

我们将为振荡器使用外部电阻器。 数据表中建议的电阻器容差为0.1%、但实际上、我们可能会有一个值略有不同/容差更差的电阻器。 因此、我们需要校准频率并记住 CSRFCAL 寄存器值。

- 每个寄存器位的含义是什么? 或者、如何校准频率(在+/-几个百分点范围内)?

- 我们假设我们可以测量 MLCK 频率(直接测量或其细分)并通过串行接口更改 CSREFCAL 中的值。

- 由于不同的原因、我们更倾向于使用16MHz 而不是16、384MHz 时钟。 这将产生1MHz 的 A/D 转换器时钟、而不是建议的1.024MHz。

- 它是否会对转换器和整个器件的运行产生负面且明显的影响?

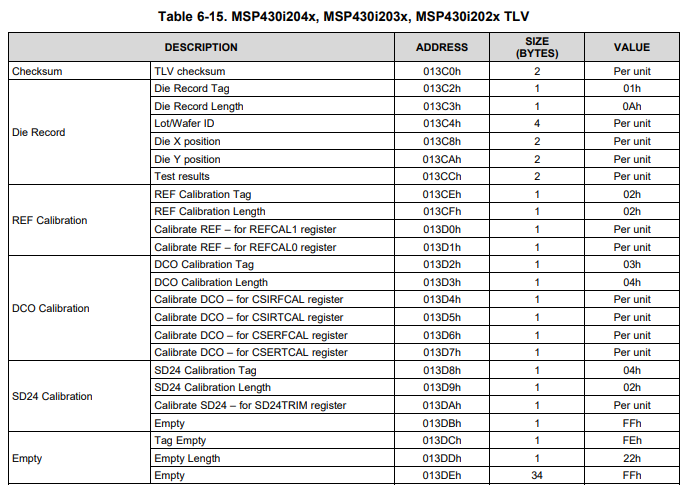

- MSP430i20xx 的主存储器中是否有任何有助于识别它们的标识符? 如果是、在哪里/如何?

- 例如、MSP430F148在0x0ff0地址下具有0xf149。

谢谢你。