各位专家、您好!

请告诉我 MSP430的 GPIO。

Q1:如果 P3.0突然从高电平变为低电平、P3.1是否可能受到内部电路的影响、从而改变引脚的状态?

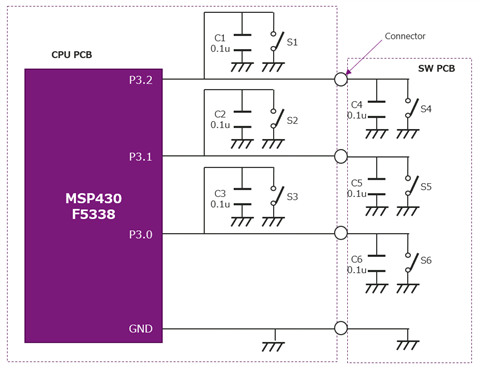

我的客户目前具有以下电路配置:带有附加软件 PCB 的 CPU PCB。安装电容器以降低噪声。

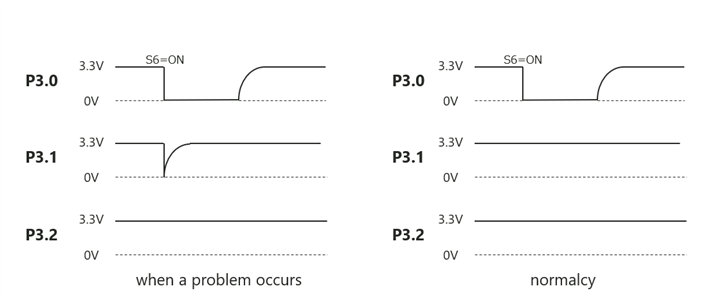

当 S6连接到 P3.0时、P3.1会暂时降低。 下图显示了问题发生时的波形、以及正常情况下的波形。

但是、当 S3设置为 ON 时、波形为"正常"。

即使 C1、2和3被删除并且 S6被打开、波形也是"正常"。

我怀疑"SW PCB"侧的布局、但我想确认对 MSP430侧的影响。

如果不是 MSP430的影响、请告诉我问题的其他可能原因。

此致、

还不错