您好...

我有一个 MSP430FR2355开发板....

如果我从 Resource Explorer 导入 msp430fr235x_CS_03.c、并运行代码并在 P1.0上监控 SMCLK、我会看到16MHz 的频率符合预期。 当我停止调试器时,时钟会继续...如果我给板加电,时钟会返回...一切都很好!

现在、如果我将以下内容加载到电路板上

SysClk_Handle_t sysClk;

#ifdef CLK_TEST

GPIO_RegDef_t *sm_a_clk_test = PORT1, *mclk_test = PORT3;

#endif

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // stop watchdog timer

/*

* System Clock / ACLK Configuration

*/

sysClk.pSysClk = CLOCK;

sysClk.SysClk_Config.Clock_MCLK = MCLK_16MHZ;

sysClk.SysClk_Config.FLL_Source = FLL_EXT_XTL;

sysClk.SysClk_Config.Clock_SMCLKDiv = SMCLK_DIVIDE1;

init_Clock(&sysClk);

#ifdef CLK_TEST

sm_a_clk_test->DIR |= BIT1 | BIT0;

sm_a_clk_test->SEL[1] |= BIT1 | BIT0;

mclk_test->DIR |= BIT0;

mclk_test->SEL[0] |= BIT0;

#endif

while(1);

}

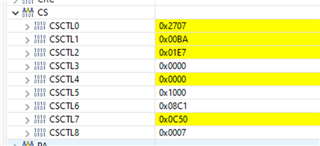

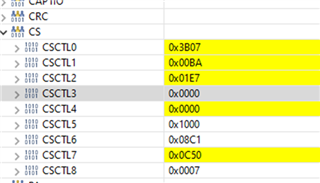

然后点击 Play 时钟会按预期上升到16MHz,但是当我停止调试器时,时钟会平稳下来并停止...如果我重新为电路板供电,时钟就永远不会再次上升。

现在有趣的部分...如果我用不起作用的代码重新刷新它、时钟永远不会出现...我首先必须用 msp430fr235x_CS_03.c 重新刷新它并运行它。 如果我执行此操作、则重新加载代码并运行、我会看到时钟。

这告诉我什么????? 是否在我的项目上设置属性????? 似乎不是代码、因为重新刷写所谓的坏代码时、我运行时钟时应允许时钟显示、而无需重新刷写演示代码???

这里的所有帮助都很好、因为我不知道该怎么想

谢谢

Steve