主题中讨论的其他器件: MSP430F5529、 MSP430F5438A

大家好、TI 论坛、

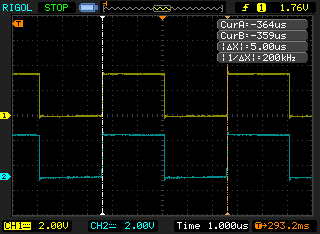

我注意到、在向上计数模式下运行和切换输出引脚模式时、TA1和 TB0之间存在差异。

两个计时器使用相同的配置(如下所示)、但我从这两个计时器获得的输出引脚频率不同。

TA1CCR0 = 9;

TA1CCTL1 = 0x0080; //TA1.1处于比较模式并切换输出引脚模式

TA1CCR1 = 5;

TA1EX0 = 0x0000; //TMRA1输入分频器扩展设置为1

TA1CTL = 0x0114;

TB0CCR0 = 9;

TB0CCTL5 = 0x0080; /TB0.5处于比较模式并切换输出引脚模式

TB0CCR5 = 5;

TB0EX0 = 0x0000; //TMRB0输入分频器扩展设置为1分频

TB0CTL = 0x0114;

两个计时器均由 ACLK 计时、在我的案例中为14.7456MHz。

TA1.1输出引脚频率(测量值)与公式 Fout = ACLK /((TA1CCR0 + 1)* 2)= 737.28KHz 一致

但是、TB0.5输出引脚频率(测量值)更高且等于819.2KHz、这与 Fout = ACLK /(TB0CCR0 * 2)= 819.2KHz 一致

如果我配置 TB0CCR0 = 10、那么两个定时器在各自的输出引脚上生成相同的频率(737.28KHz)。

您能解释一下这种行为吗?