主题中讨论的其他器件: MSP430FR2311、 MSP-TS430PW20、 MSP-FET430UIF

大家好、

使用 MSP430FR2110

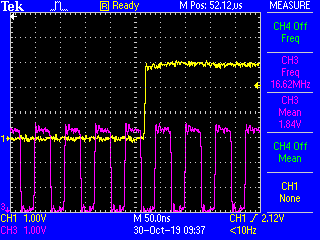

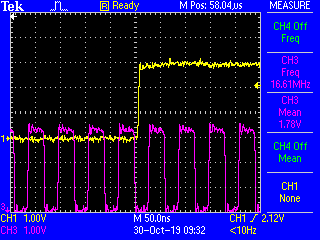

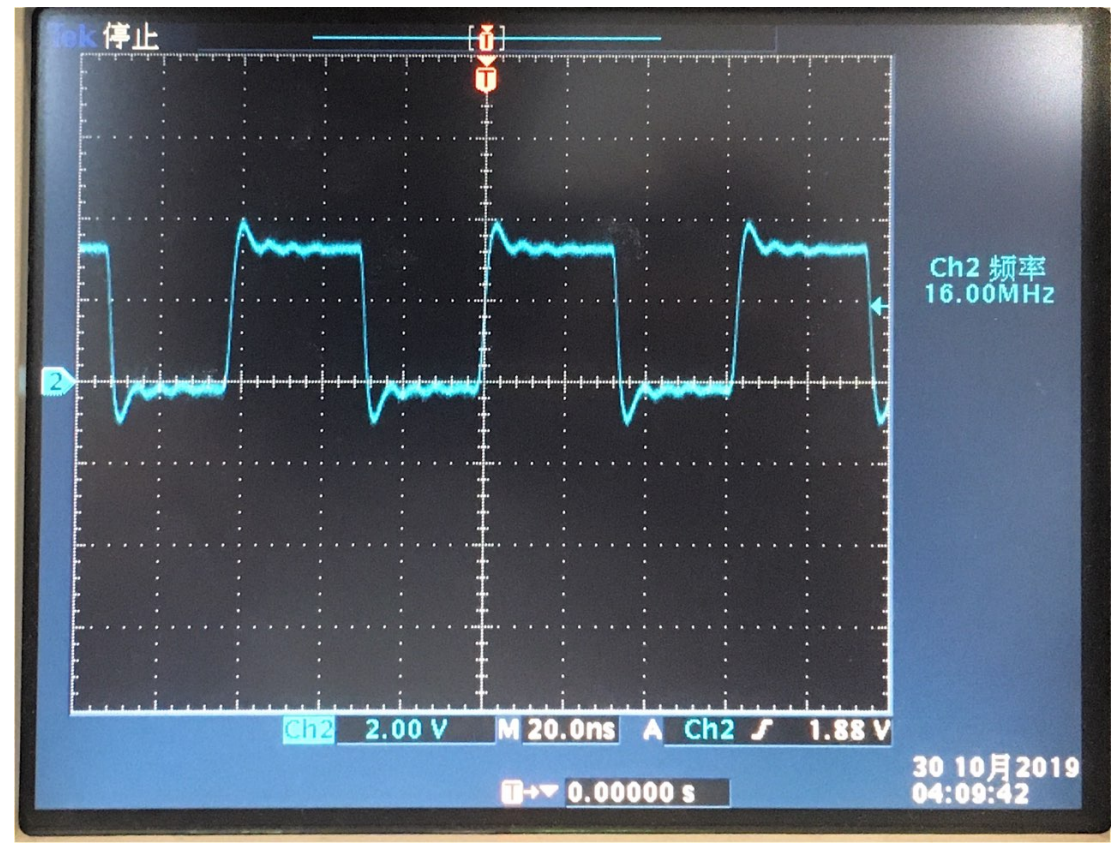

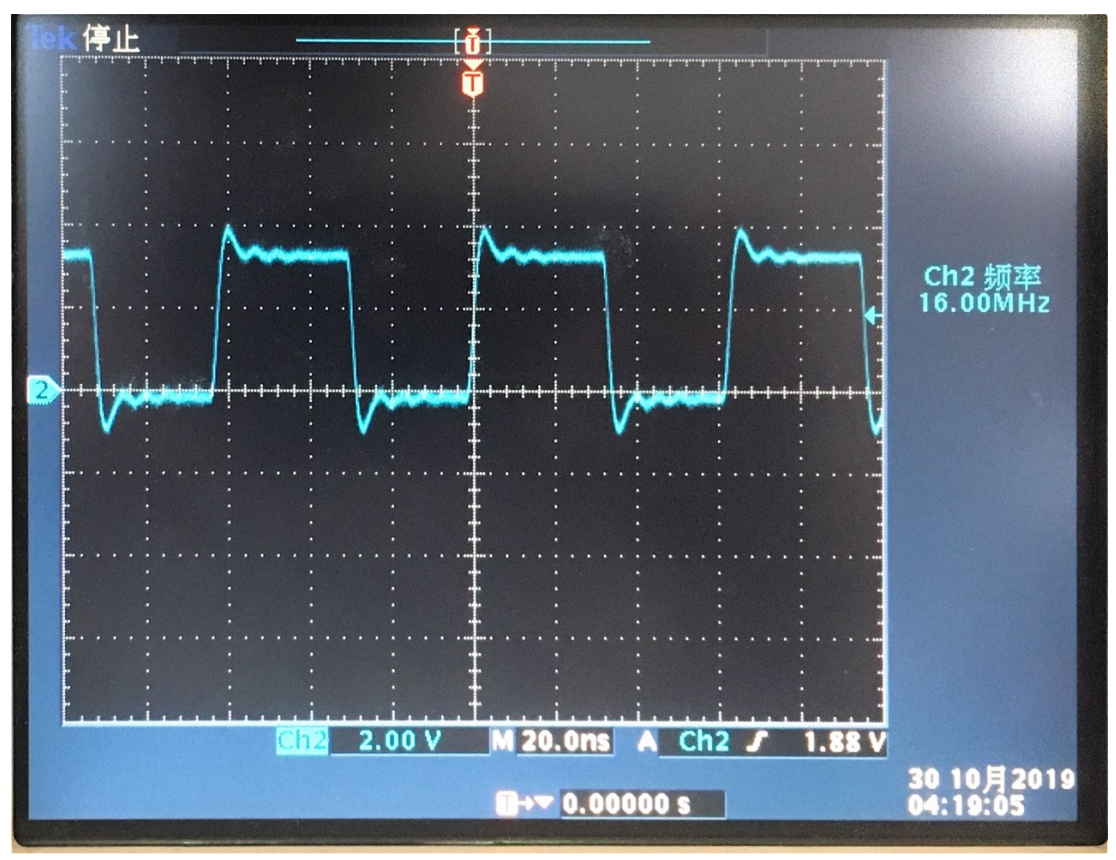

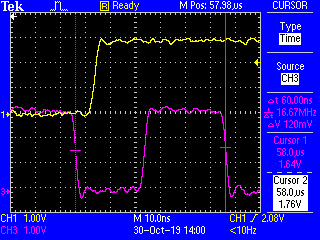

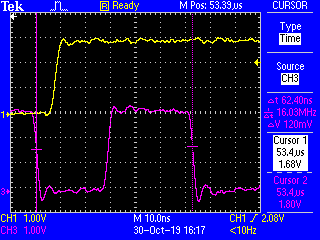

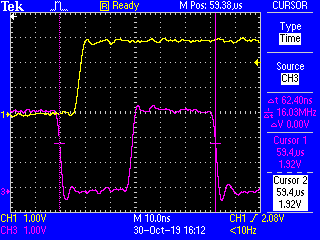

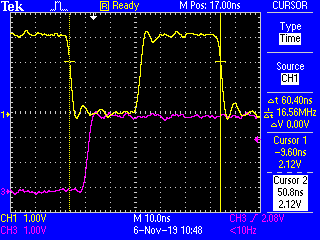

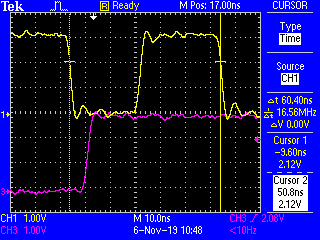

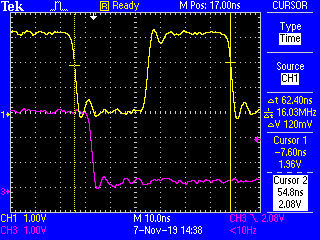

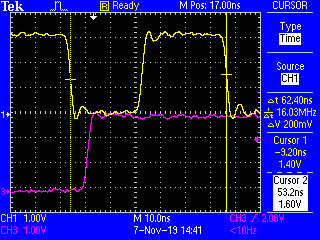

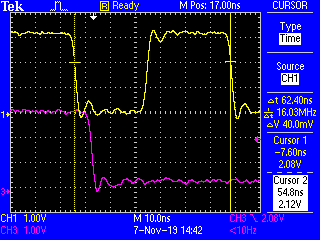

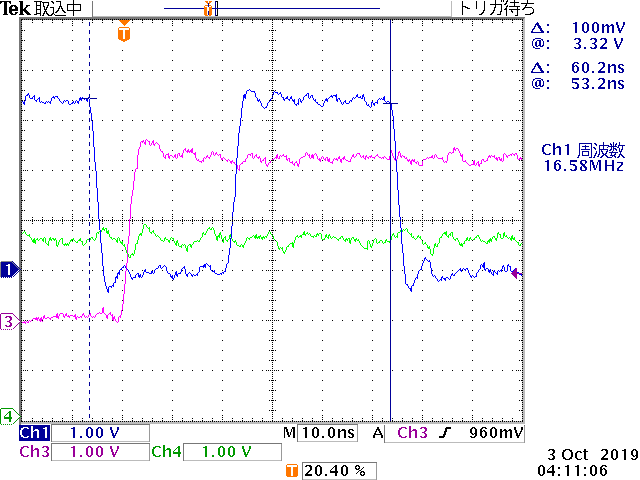

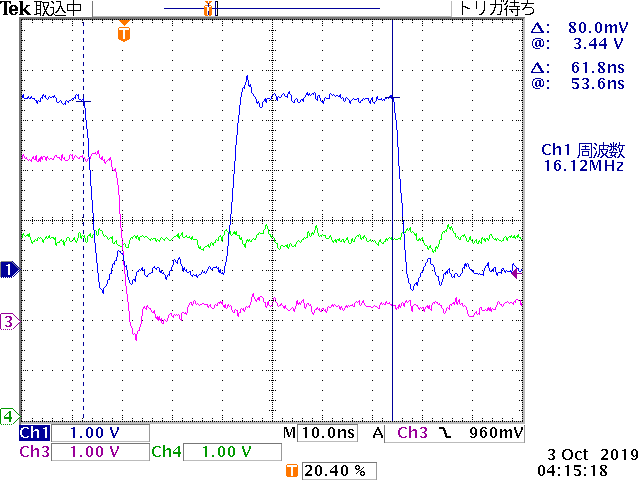

我希望将从上电到 P1.0的时间设置为"高电平" 40ms 或更短。 MCLK 必须为16MHz。

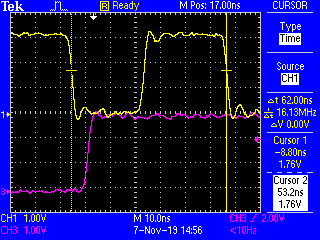

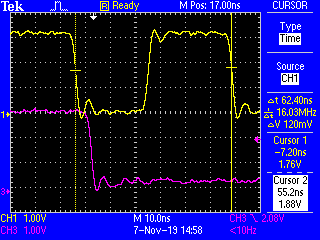

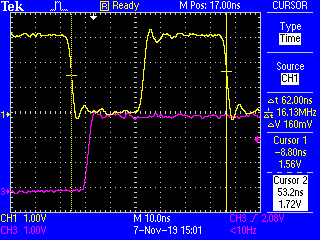

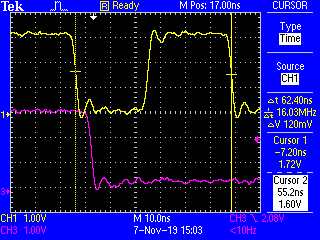

当前软件需要138ms 的处理时间。

有关 DCO 软件调整的更多信息

我参考了 MSP430硬件工具用户指南.pdf。

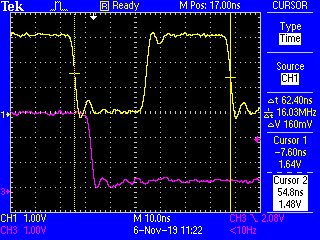

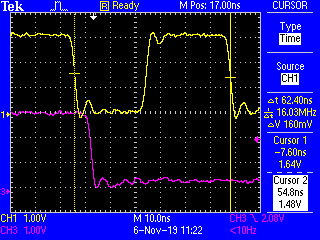

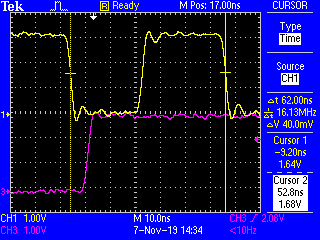

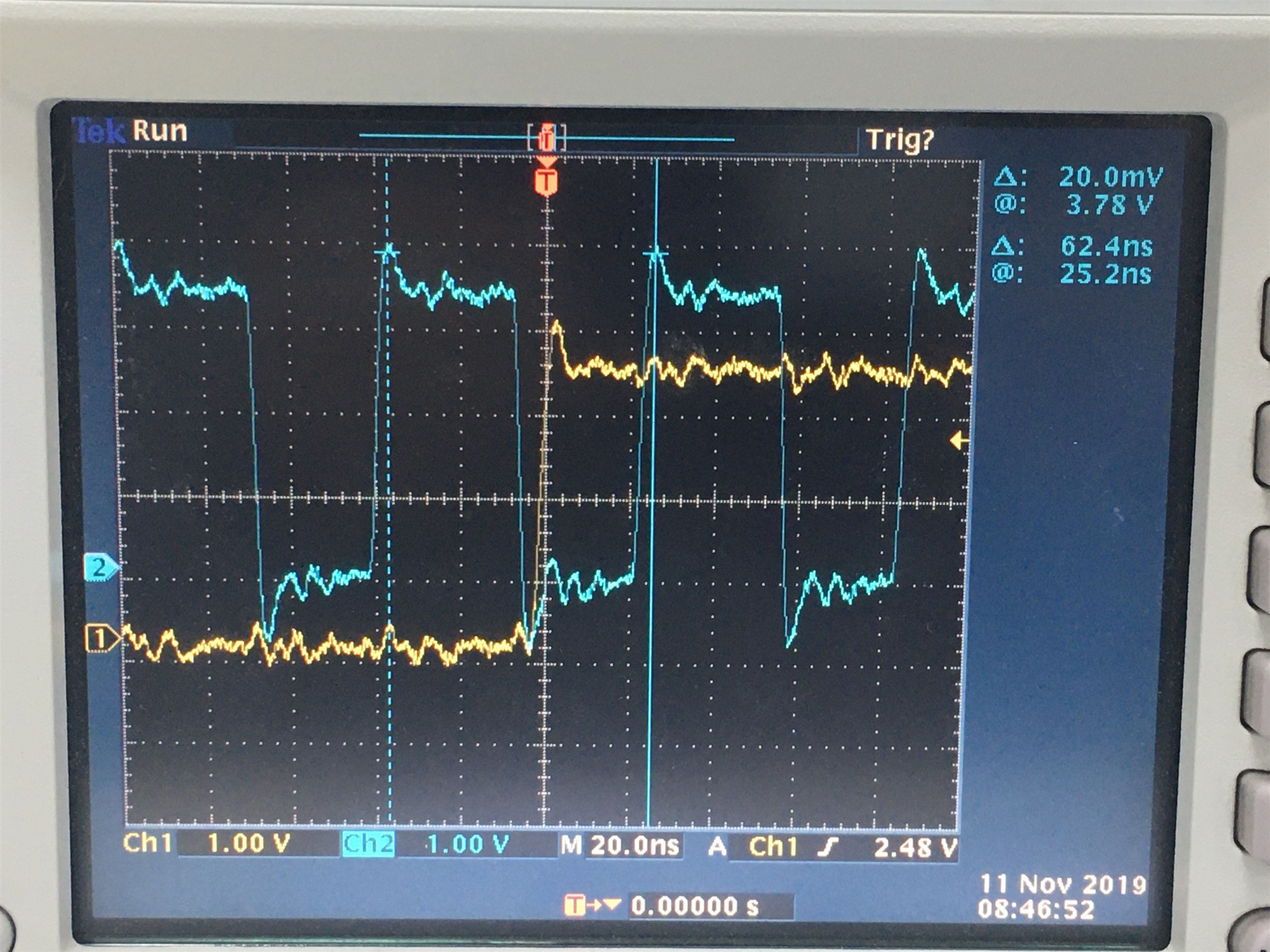

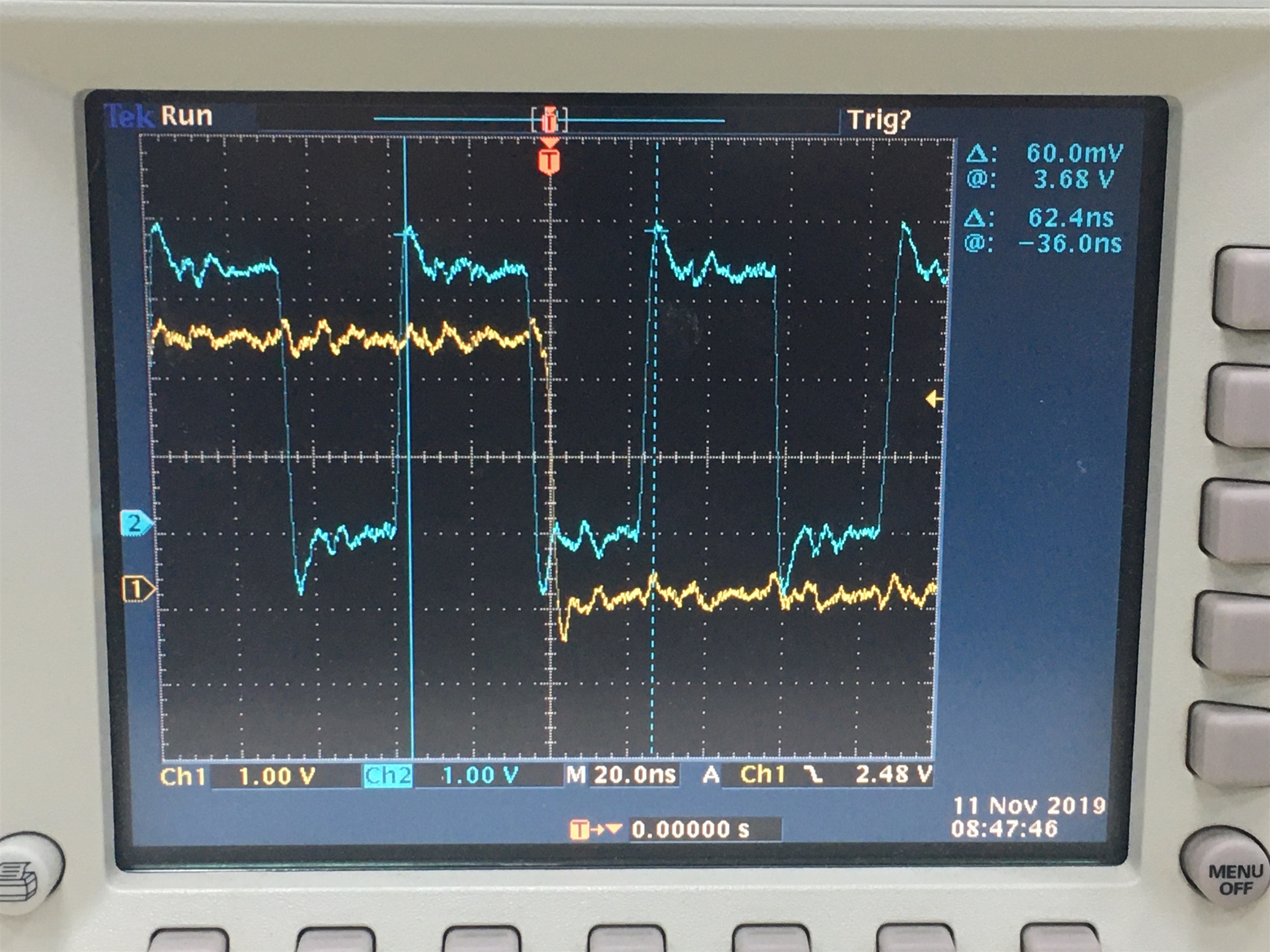

在 Software_Trim ()处理上花费了47ms 的时间。

-如果您在不等待 FLL 锁定的情况下执行处理、您会有什么顾虑?

-请就如何增加启动时间向我提供建议。

int main (空)

{

/* 端口1初始化*/

P1DIR = 0x31;

P1REN = 0x08;

P1OUT = 0x00;

P1SEL0 = 0x02;

P1SEL1 = 0xC2;

P1IES = 0x08;// P1.3中断低边沿*/

P1IE = 0x08;/* P1.3中断使能*/

WDTCTL = WDTPW + WDTHOLD; //停止看门狗计时器*/

PM5CTL0 &=~LOCKLPM5; //禁用 GPIO 上电默认高阻抗模式

//激活先前配置的端口设置

FRCTL0 = FRCTLPW | NWAITS_1; //将 FRAM 等待状态设置为1 */

Clock_setting();

__bis_SR_register ( GIE ); //启用中断*/

P1OUT |= 0x01;

while (1){}

}

空 Clock_setting()

{

_bis_SR_register (SCG0); //禁用 FLL

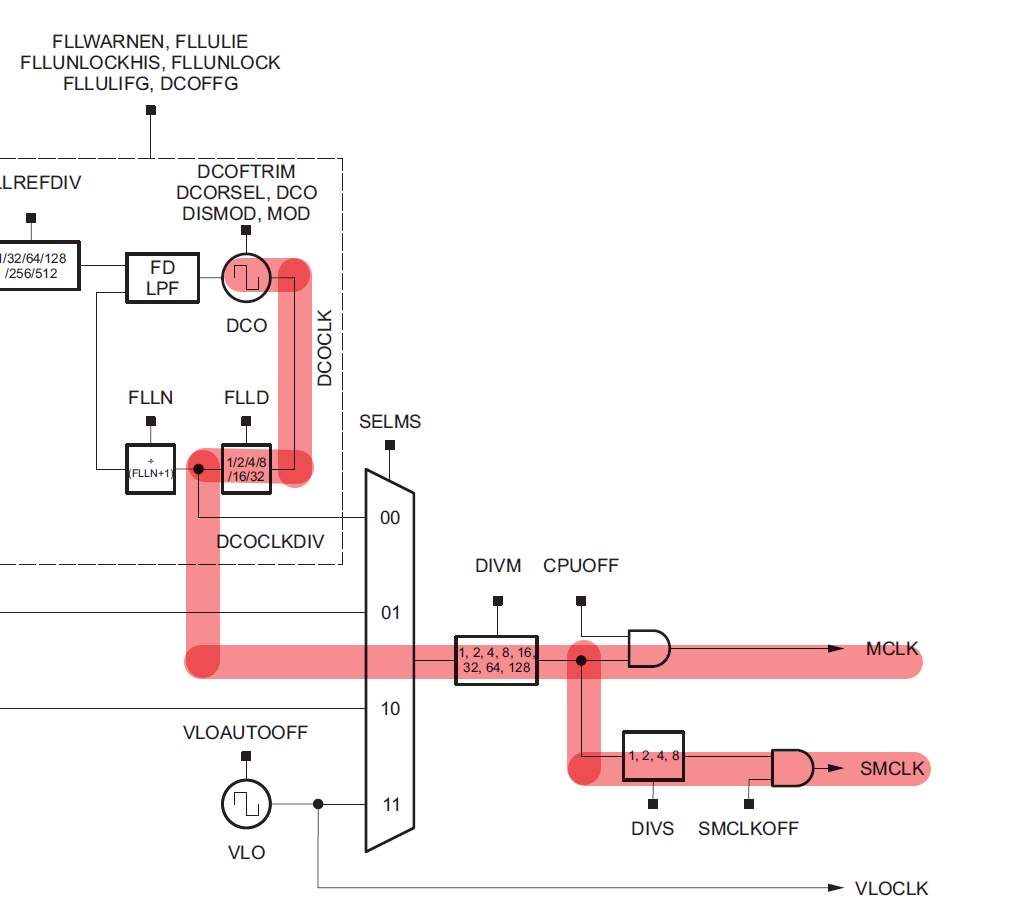

CSCTL3 |= SELREF_REFOCLK; //将 REFO 设置为 FLL 基准源

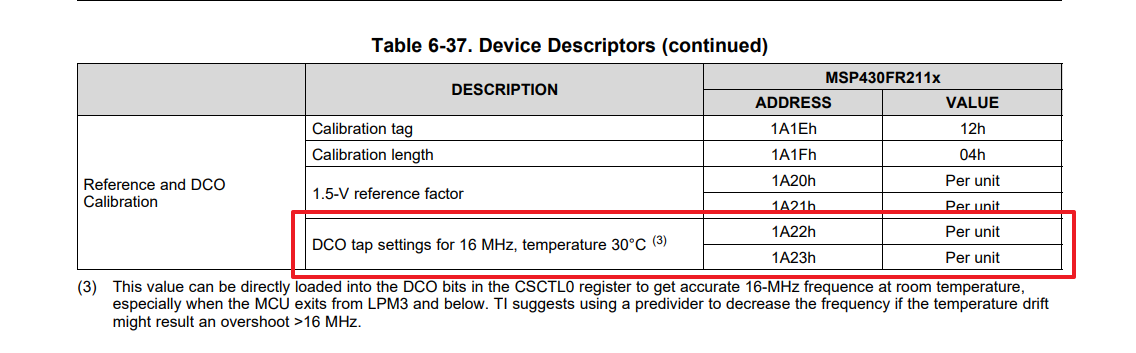

CSCTL1 = DCOFTRIMEN_1 | DCOFTRIM0 | DCOFTRIM1 | DCORSEL_5;// DCOFTRIM = 3、DCO 范围= 16MHz

CSCTL2 = FLLD_0 + 488; // DCODIV = 16.023552MHz

_DELAY_CYCLES (3);

_BIC_SR_register (SCG0); //启用 FLL

Software_Trim (); //软件调整可获得最佳 DCOFTRIM 值

CSCTL4 = SELMS_DCOCLKDIV | SELA_REFOCLK;//将默认 REFO (~32768Hz)设置为 ACLK 源、ACLK = 32768Hz

//默认 DCODIV 为 MCLK 和 SMCLK 源

}

空 Software_Trim ()

{

unsigned int oldDcotTap = 0xFFFF;

unsigned int newDcoTap = 0xFFFF;

unsigned int newDcoDelta = 0xFFFF;

unsigned int bestDcoDelta = 0xFFFF;

unsigned int csCtl0Copy = 0;

unsigned int csCtl1Copy = 0;

无符号 int csCtl0Read = 0;

无符号 int csCtl1Read = 0;

unsigned int dcoFreqTrim = 3;

unsigned char endLoop = 0;

操作

{

CSCTL0 = 0x100; // DCO 抽头= 256

操作

{

CSCTL7 &=~DCOFFG; //清除 DCO 故障标志

} while (CSCTL7 & DCOFFG); //测试 DCO 故障标志

if (MCLK =MCLK16MHz)__DELAY_CYCLLES ((unsigned int) 3000 * 16);//等待 FLL 锁定状态(FLLUNLOCK)保持稳定

//建议等待24个经过分频的 FLL 参考时钟周期

while (((CSCTL7 &(FLLUNLOCK0 | FLLUNLOCK1))和&((CSCTL7 & DCOFFG)= 0));

CSCCtl0Read = CSCTL0; //读取 CSCTL0

CSCCtl1Read = CSCTL1; //读取 CSCTL1

oldDcoTap = newDcoTap; //记录上次的 DCOTAP 值

newDcoTap = csCtl0Read & 0x01ff; //这次获得 DCOTAP 值

dcoFreqTrim =(csCtl1Read & 0x0070)>>4;//获取 DCOFTRIM 值

if (newDcoTap < 256) // DCOTAP < 256

{

newDcoDelta = 256 - newDcoTap; // DCPTAP 和256之间的增量值

if ((oldDcotap!= 0xFFFF)&&(oldDcotap >= 256)// DCOTAP 交叉256

endLoop = 1; //停止 while 循环

其他

{

dcoFreqTrim --;

CSCTL1 =(csCtl1Read &(~DCOFTRIM))|(dcoFreqTrim <4);

}

}

else // DCOTAP >= 256

{

newDcoDelta = newDcoTap - 256; // DCPTAP 和256之间的增量值

if (oldDcoTap < 256) // DCOTAP 交叉256

endLoop = 1; //停止 while 循环

其他

{

dcoFreqTrim++;

CSCTL1 =(csCtl1Read &(~DCOFTRIM))|(dcoFreqTrim <4);

}

}

if (newDcoDelta < bestDcoDelta) //记录最接近256的 DCOTAP

{

csCtl0Copy = csCtl0Read;

csCtl1Copy = csCtl1Read;

bestDcoDelta = newDcoDelta;

}

}while (endLoop =0); //轮询直至 endLoop =1

CSCTL0 = csCtl0Copy; //重新加载锁定的 DCOTAP

CSCTL1 = csCtl1Copy; //重新加载锁定的 DCOFTRIM

while (CSCTL7 &(FLLUNLOCK0 | FLLUNLOCK1));//轮询直到 FLL 被锁定

}

提前做好准备。

此致、

K.Saito