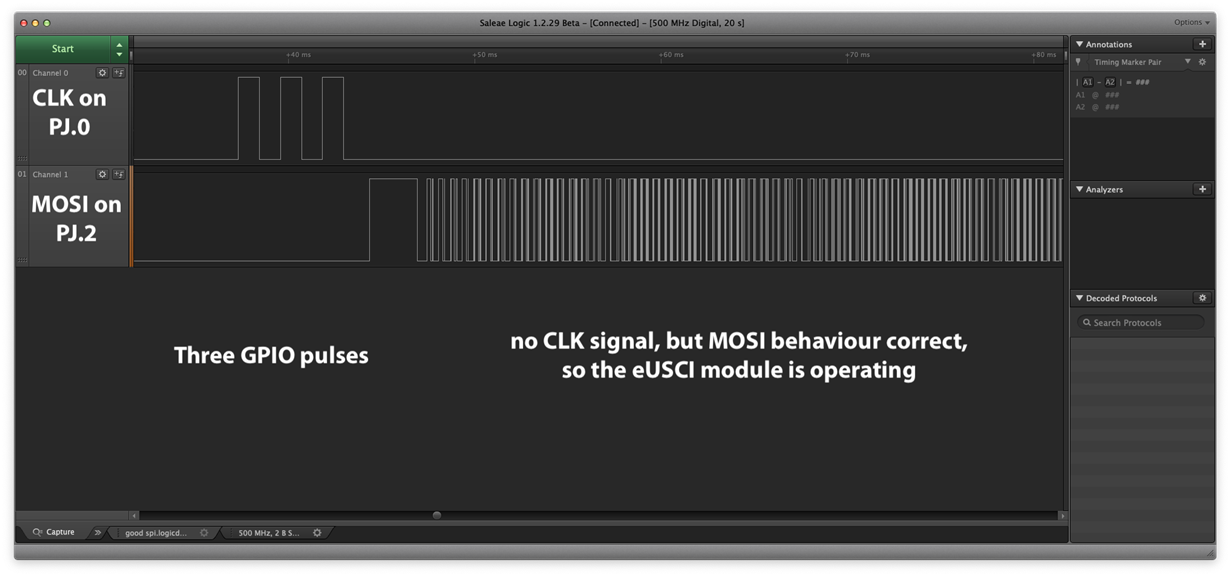

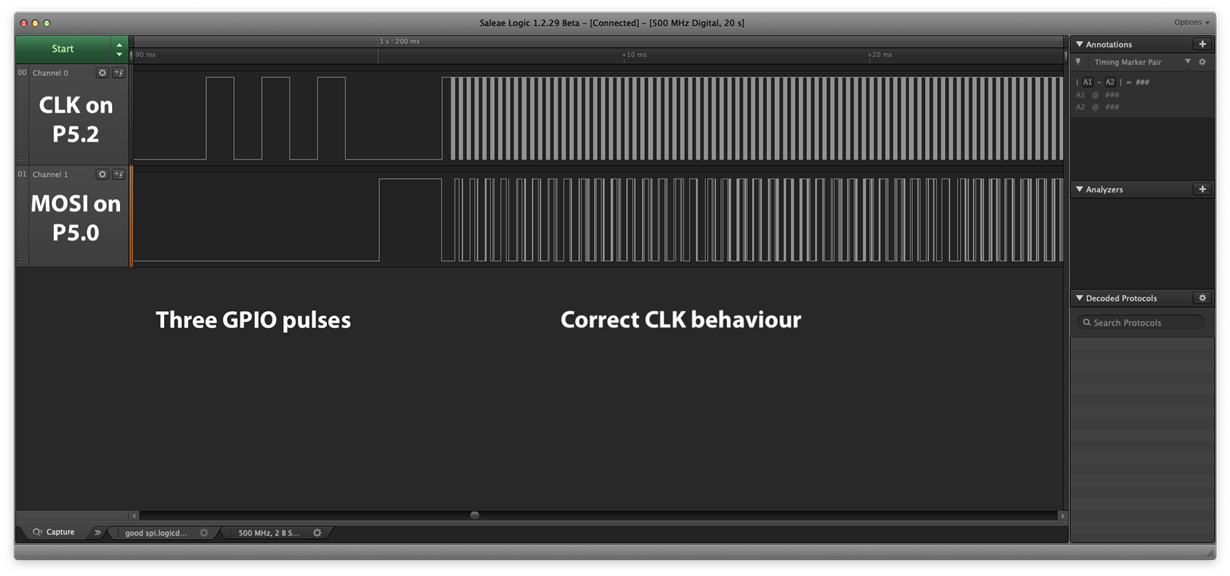

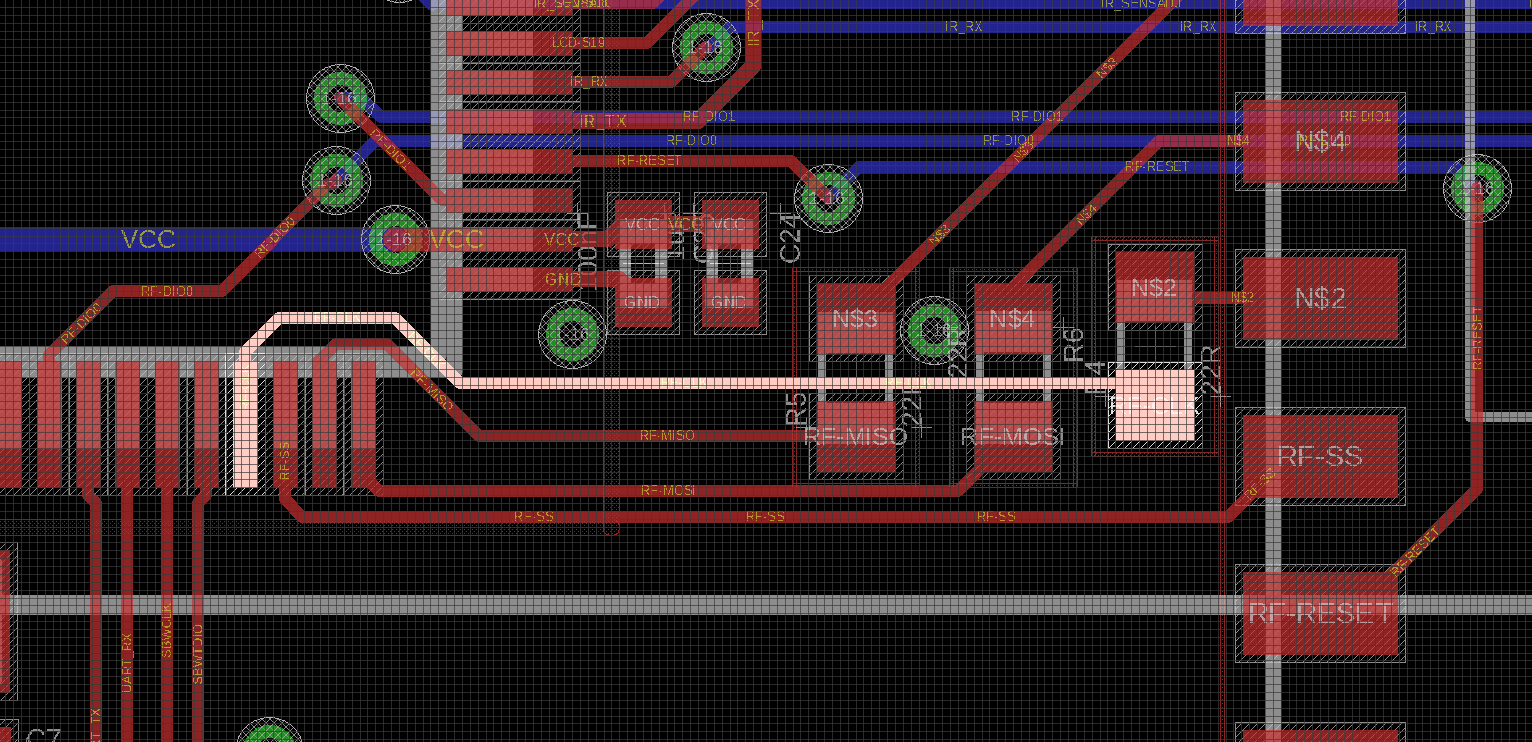

在尝试将 MSP430FR6043映射到端口 PJ (引脚 PJ.0-PJ.3)时、我遇到了 MSP430FR6043上的 SPI 功能问题。 PJ.2上的 MOSI 信号工作正常、但时钟根本不会出现在 PJ.0上。 当映射到端口 P5 (P5.0 - P5.3)时、一切都按预期工作。 我通过将 PJ.0设置为数字 IO 并发送一些在示波器上正确记录的脉冲来仔细检查电气连接。 我在三个单独的器件上重复了此测试、结果相同。 我在连接 SPI 器件和 MCU 引脚悬空的情况下尝试了这两种方法。 我认为端口 PJ 上的引脚未进入 JTAG 模式、SYSJTAGPIN 为0、并且在使用 SPW 进行调试以及在 SPW 编程器断开连接且 RESET 引脚始终拉高的情况下依靠电池运行时、器件的行为是相同的。 是否还有其他因素阻止 PJ.0引脚多路复用为 UCA2模块上的 SPI 时钟? 请提供建议。 我非常希望这些引脚能够专门用于该功能、因为我正在使用非常紧凑的 PCB 布局、并且 USS 模块和 LCD 的位置是固定的、这给我留下了很小的回旋空间。

已连接:引脚 P5.2 (有效)和 PJ.0 (无效)的示波器迹线、以及我运行的测试代码。 这些测试在自定义 PCB 上执行、PJ.0引脚悬空(仅连接到示波器探针)、或连接到一个认为为22R 电阻的 SPI 从器件。 调试了 MSP FET、通过 SBW 连接、仅连接 SBWCLK 和 SBWTDO 引脚。 感谢您的任何反馈!

#include "driverlib.h" uint8_t RXData = 0; uint8_t TXData = 0; int i=0; void main (void){ //停止看门狗计时器 WDT_A_HOLD (WDT_A_base); PMM_unlockLPM5 (); //将 DCO 频率设置为最大 DCO 设置 CS_setDCOFreq (CS_DCORSEL_0、CS_DCOFSEL_3); CS_initClockSignal (CS_SMCLK、CS_DCOCLK_SELECT、CS_Clock_divider); //测试输出模式中的 CLK 引脚 GPIO_setAsOutputPin (GPIO_PORT_PJ、BIT0); GPIO_setAsOutputPin (GPIO_PORT_P5、BIT2); //3个脉冲 for (i=0;i<6;i++){ GPIO_toggleOutputOnPin (GPIO_PORT_PJ、BIT0); GPIO_toggleOutputOnPin (GPIO_PORT_P5、BIT2); __DELAY_CYCLES (1000); } //对于端口 PJ (CLK 不工作) GPIO_setPeripheralModuleFunctionInputPin (GPIO_PORT_PJ、BIT0 | BIT1 | BIT2 | BIT3、GPIO_PRIMARY_MODULE_FUNCTION); //对于端口 P5 (工作正常) GPIO_setPeripheralModuleFunctionInputPin (GPIO_PORT_P5、BIT0 | BIT1 | BIT2 | BIT3、GPIO_secondary 模块_function); //初始化主设备 EUSCI_A_SPI_initMasterParam param ={0}; param.selectClockSource = EUSCI_A_SPI_CLOCKSOURCE_SMCLK; param.clockSourceFrequency = CS_getSMCLK(); param.desiredSpiClock = 50000; param.msbFirst = EUSCI_A_SPI_MSB_FIRST; param.clockPhase = EUSCI_A_SPI_PHASE_DATA_Changed_ONFIRST_capted_on_next; param.clockPolarity = EUSCI_A_SPI_CLOCKPOLARITY_INACT_HIGH; param.spiMode = EUSCI_A_SPI_3引脚; EUSCI_A_SPI_initMaster (EUSCI_A2_base、¶m); //启用 SPI 模块 EUSCI_A_SPI_ENABLE (EUSCI_A2_BASE); EUSCI_A_SPI_clearInterrupt (EUSCI_A2_base、EUSCI_A_SPI_Receive_interrupt); //启用 USCI_A0 RX 中断 EUSCI_A_SPI_enableInterrupt (EUSCI_A2_base、EUSCI_A_SPI_receive_interrupt); //等待从器件初始化 _DELAY_CYCLES (100); TXData = 0x1; //保留 TX 数据 //USCI_A0 TX 缓冲器准备好了吗? while (!eUSCI_A_SPI_getInterruptStatus (eUSCI_A2_base、eUSCI_A_SPI_Transmit 中断)); //向从器件发送数据 EUSCI_A_SPI_transmitData (EUSCI_A2_base、TXData); _bis_SR_register (LPM0_bits + GIE); // CPU 关闭,启用中断 __no_operation(); //保持在 LPM0 中} #pragma vector=USCI_A2_vector __interrupt void USCI_A2_ISR (void){ 开关(__evo_in_range (UCA2IV、USCI_SPI_UCTXIFG)) { USCI_SPI_UCRXIFG 案例: // UCRXIFG //USCI_A0 TX 缓冲器准备好了吗? while (!eUSCI_A_SPI_getInterruptStatus (eUSCI_A2_base、eUSCI_A_SPI_Transmit 中断)); RXData = EUSCI_A_SPI_receiveData (EUSCI_A2_base); //递增数据 TXData++; //发送下一个值 EUSCI_A_SPI_transmitData (EUSCI_A2_base、TXData); //从机处理信息的传输之间的延迟 _DELAY_CYCLES (40); 中断; 默认值: 中断; } }