主题中讨论的其他器件:ENERGYTRACE

您好!

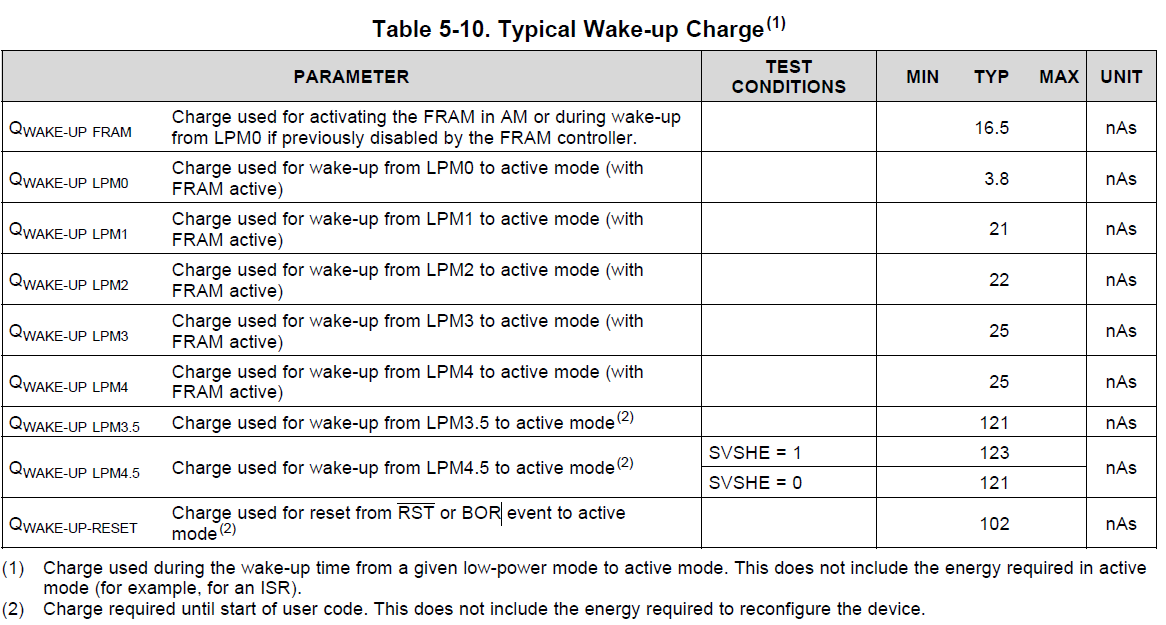

我尝试了解数据表中的唤醒数字。 我从 LPM3唤醒的测量值大约为23nC、接近下图(但对额外的 FRAM 唤醒电荷有点困惑)。

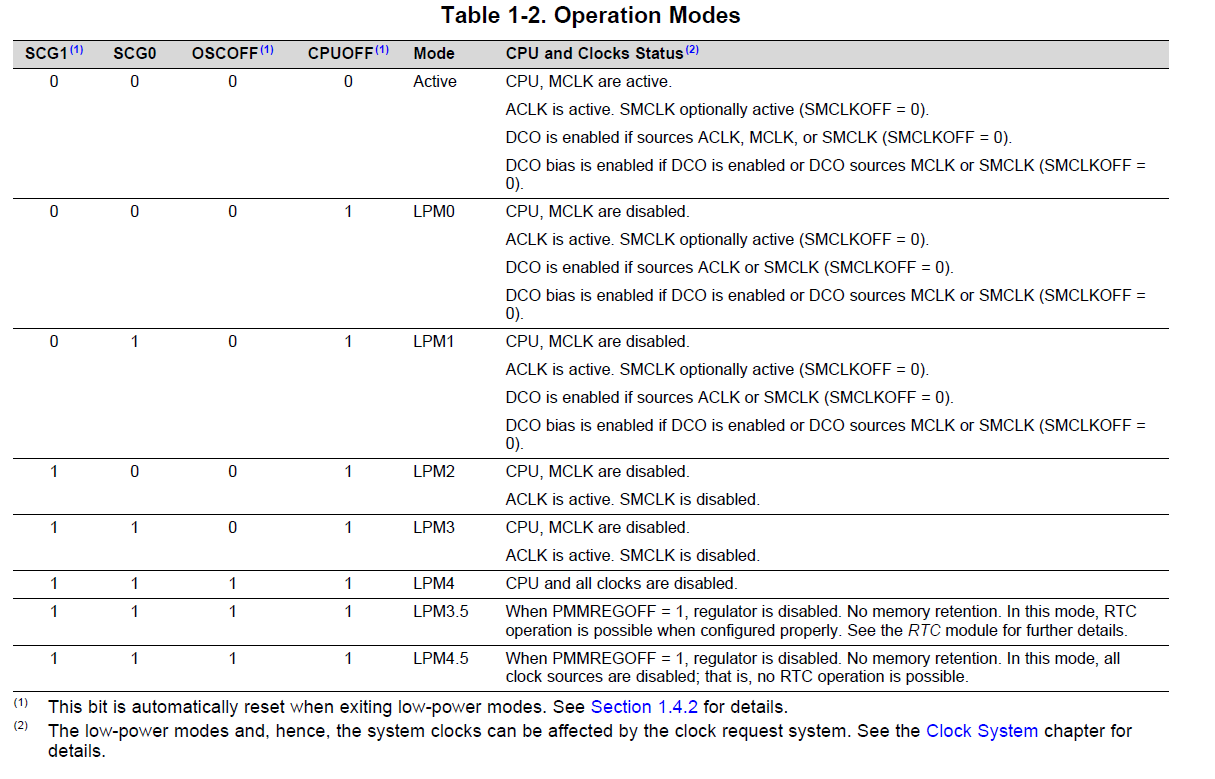

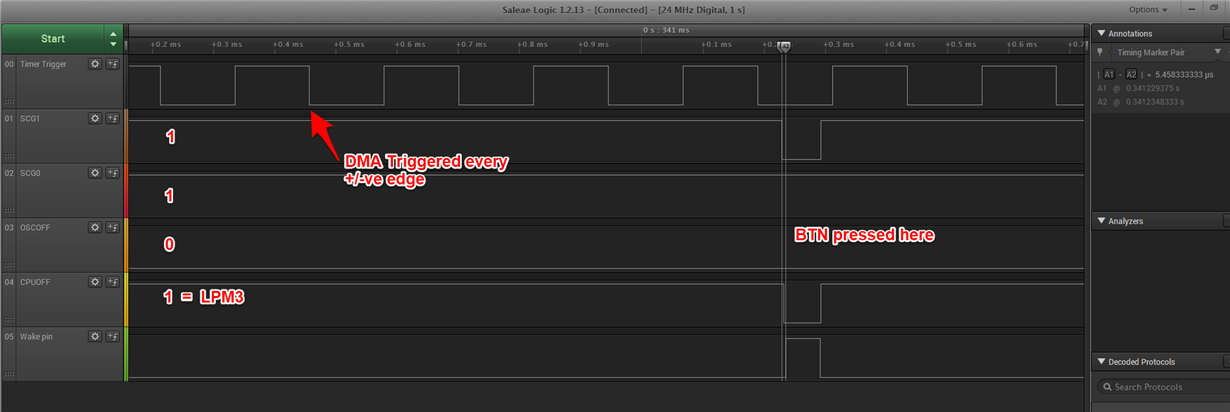

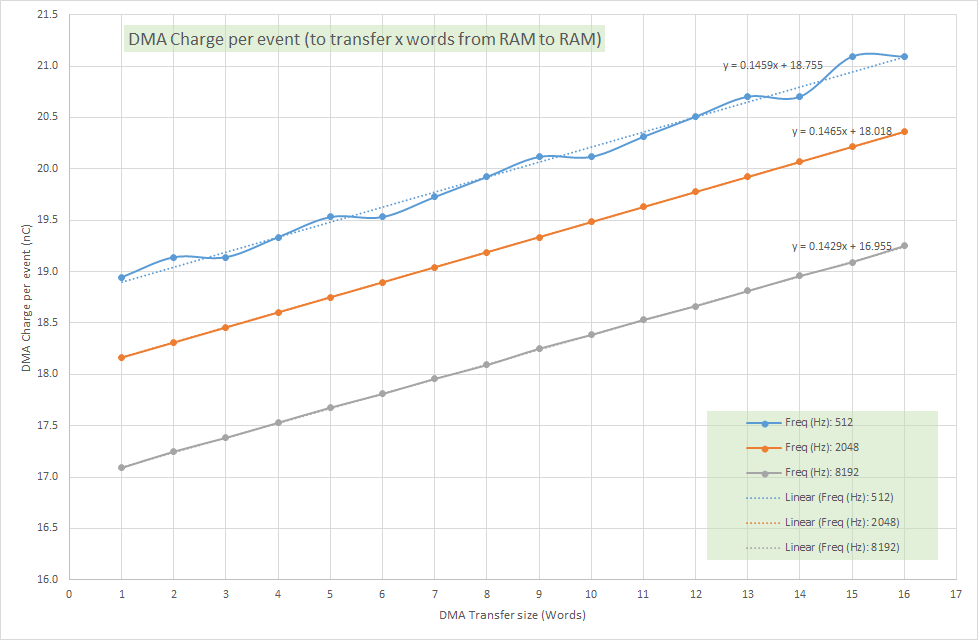

我已经编写了其他代码来使用 DMA 将字节从一个 RAM 位置传输到另一个 RAM 位置、从 LPM3使用 ALCK->TIMRB 来触发它。 除按下按钮外、没有中断。 IM、对于 M/SMCLK 使用8MHz。

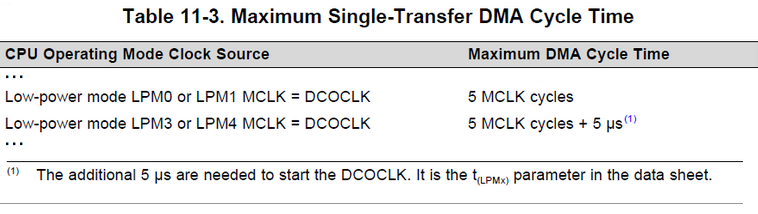

我在18nC 左右测量以唤醒 DMA。 但我认为它会更低。 虽然、比较表1-2 (寄存器位)和表5-10 (唤醒电荷)中的 LPM0和 LPM3、它们唤醒之间的区别是重新配置 DCO/MCLK。 通用性是唤醒 CPU。 因此、从 LPM3的 DMA 唤醒电荷应该与 QWAKE (LPM3)- QWAKE (LPM0)相似、因为 DMA 必须唤醒/配置 DCO、请求总线时钟、但不会唤醒 CPU。

因此、预期的唤醒电荷为25-3.8=21.2nC:

预期 QWAKE (DMA)~ 21nC

我是否正确理解了这一点?

此外、基于下表的 LPM3唤醒时间(基于3个周期、因为我忽略每次传输的2个周期)将为5.375us。 8MHz 时 LPM3->有效的唤醒时间为6.85us。

5.375/6.85 * 23nC = 18nC、这似乎也是一个很强的线索。

我配置了 PJ.x 位来输出 SR 位。 它们不会改变、但我想这是预料之中的、DMA 会根据需要控制位来唤醒 DCO/MCLK 时钟? 用户指南指出 SCG1/0与器件相关、SCG1"例如"是 DCO 偏置使能、SCG0"例如"是 FLL 使能。 当然想知道、但在数据表中找不到任何内容。

数据表图:

FRAM 唤醒= 16.5nC。

LPM0唤醒= 3.8nC

LPM3唤醒= 25nC

测量值(在不同频率(a)下测量平均电流、然后除以频率(1/s)、以获取每个事件的电荷(AS)):

LPM3唤醒~= 23nC

DMA ~= 18nC (y 从下面截取)

谢谢。